**Consortium For On-Board Optics**

# **COBO 8-Lane & 16-Lane On-Board Optics Specification**

Release 1.1

This specification defines the characteristics of 8 and 16 lane On-Board Optics (OBO) for use in up to 1x 400G and 2x 400G applications and provides a common specification for systems manufacturers, system integrators, component manufacturers, and suppliers of on-board optics.

## **REVISION HISTORY:**

| Version | Date               | Co-Packaged Optics                   |

|---------|--------------------|--------------------------------------|

| 0.1     | June 04, 2016      | Adopted Baseline Draft               |

| 0.2     | July 27, 2017      |                                      |

| 0.3     | August 08, 2017    | Approved Baseline Draft              |

| 0.4     | September 05, 2017 | Specification Draft 0.4              |

| 0.5     | October 13, 2017   | Specification Draft 0.5              |

| 0.6     | December 08, 2017  | Specification Draft 0.6              |

| 0.7     | December 18, 2017  | Specification Draft 0.7              |

| 0.8     | December 22, 2017  | Specification Draft 0.8              |

| 0.9     | January 24, 2018   | Specification Draft 0.9              |

| 0.91    | January 30, 2018   | Approval Draft 0.91                  |

| 1.0     | February 26, 2018  | Approved Specification (Release 1.0) |

| 1.01    | June 24, 2018      | Draft 1.01                           |

| 1.02    | September 20, 2018 | Draft 1.02                           |

| 1.03    | September 27, 2018 | Approval Draft 1.03                  |

| 1.1     | December 09, 2018  | Approved Specification (Release 1.1) |

## **POINTS OF CONTACT:**

Jeffery J. Maki, Juniper Networks, Data Center Networking (DCN) Working Group Chairman, jmaki at juniper.net

Hugues Tournier, Ciena, DCN Working Group, Electrical Sub-Group Chairman, htournie at ciena.com

**Tom Mitcheltree,** USCONEC, DCN Working Group, Optical Connectivity Editor, tommitcheltree at USConec.com

Jeff Hutchins, Ranovus, DCN Working Group, Mechanical Sub-Group Chairman and Technical Editor, jeff at ranovus.com

Arlon Martin, Mellanox, DCN Working Group, Use Case and Reliability Chairman, arlonm at mellanox.com

Nasser Ghassemi, Ciena, DCN Working Group, Technical Editor, nghassem at ciena.com

Melissa Kallos - (melissa@onboardoptics.org), Consortium for On-Board Optics, Executive Editor

# COBO DATA CENTER NETWORKING WORKING GROUP MEMBERS:

| 3M Company                                          | HUBER+SUHNER AG                       |

|-----------------------------------------------------|---------------------------------------|

| ADVA Optical Networking SE                          | IBM Corporation                       |

| Alibaba Group                                       | Innovative Micro Technology           |

| Applied Optoelectronics Inc                         | Innovium, Inc.                        |

| Arista                                              | Inphi Corporation                     |

| Broadcom                                            | Juniper Networks                      |

| Celestica Inc.                                      | Kaiam                                 |

| Ciena Corporation                                   | Lumentum                              |

| Cisco                                               | Luxshare Precision Industry Co., Ltd. |

| CommScope Of North Carolina                         | Mellanox Technologies                 |

| Dell Inc.                                           | Microsoft                             |

| Dust Photonics                                      | Molex Electronic Technologies LLC     |

| Finisar Corporation                                 | nanoPrecision Products, Inc.          |

| Fujikura Ltd.                                       | NEC Corporation                       |

| Fujitsu Optical Components                          | Oclaro                                |

| Furukawa Electric                                   | PETRA                                 |

| Globalfoundries                                     | Quanta Computer Inc.                  |

| Hisense Broadband Multimedia Technologies Co., Ltd. | RANOVUS                               |

# COBO DATA CENTER NETWORKING WORKING GROUP MEMBERS: (CON'T)

| Reichle & De-Massari AG       | Sicoya GmbH                         |

|-------------------------------|-------------------------------------|

| Rosenberger North America     | STMicroelectronics International NV |

| Samtec                        | Sumitomo Electric Industries        |

| Semtech                       | TE Connectivity Corporation         |

| SENKO Advanced Components     | US Conec Ltd.                       |

| Shenzhen Gigalight Technology | Yamaichi Electronics                |

# TABLE OF CONTENTS

| Revision History                                   | 2    |

|----------------------------------------------------|------|

| COBO Data Center Networking Working Group Members: | 3    |

| Table of Contents                                  | 5    |

| Figures & Tables                                   | 8    |

| Figures                                            | 8    |

| Tables                                             | . 10 |

| Terms and Definitions                              | . 11 |

| References                                         | . 13 |

| 1.0 Introduction                                   | . 14 |

| 1.1 Scope                                          | . 14 |

| 1.2 Data Center Reference Application              | . 14 |

| 1.3 OBO Configurations                             | . 15 |

| 1.4 High-Speed Electrical Configurations           | . 16 |

| 1.5 Optical Configurations                         | . 16 |

| 1.6 Management Interface                           | . 16 |

| 2.0 Electrical Specifications                      | . 17 |

| 2.1 Purpose and Applications                       | . 17 |

| 2.2 Clocking Considerations                        | . 18 |

| 2.2.1 Data Path Description                        | . 18 |

| 2.2.2 Tx Clocking Considerations                   | . 18 |

| 2.2.3 Rx Clocking Considerations                   | . 18 |

| 2.3 Electrical Connector – High-Speed              | . 18 |

| 2.3.1 Rx(n) (p/n)                                  | . 18 |

| 2.3.2 Tx(n)(p/n)                                   | . 19 |

| 2.3.3 Eight-Lane High-Speed Pins                   | . 19 |

| 2.3.4 Sixteen-Lane High-Speed Pins                 | . 23 |

| 2.4 Electrical Connector – Low-Speed               | . 27 |

| 2.4.2 Eight and Sixteen Low-Speed Pins Locations   | . 30 |

| 2.4.3 Application Schematic                        | . 34 |

| 2.4.4 Low-Speed Electrical Specifications          | . 38 |

| 2.4.5 Timing for Soft Control and status Functions | . 39 |

| 2.4.6 Squelch and Disable Timing                   | . 40 |

# TABLE OF CONTENTS (CONT')

| 2.5 Power Supply                                                            |    |

|-----------------------------------------------------------------------------|----|

| 2.5.1 OBO Hot Pluggability                                                  |    |

| 2.5.2 OBO Power Supply Noise Output                                         |    |

| 2.5.3 OBO Power Supply Noise Tolerance                                      |    |

| 2.5.4 Return path Isolation                                                 |    |

| 2.5.5 OBO Power Sequencing                                                  |    |

| 2.5.6 OBO Power Supplies Requirements                                       |    |

| 2.5.7 Host Board Power Supply Noise Output                                  |    |

| 2.6 Management Interface Specifications                                     |    |

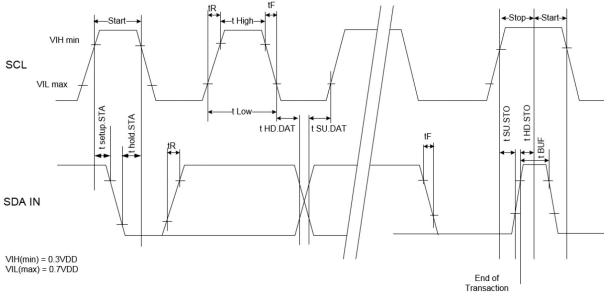

| 2.6.1 TWI Timing Specifications                                             |    |

| 3.0 Optical Connectivity                                                    |    |

| 3.1 Purpose                                                                 |    |

| 3.2 Scope                                                                   |    |

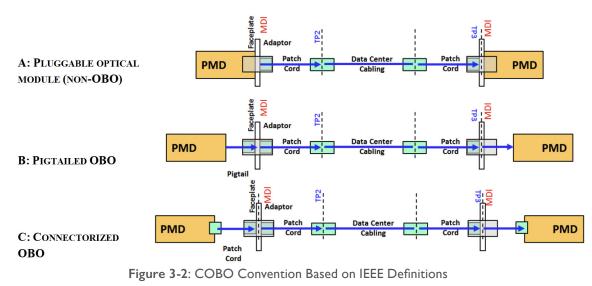

| 3.3 COBO Optical Link Convention                                            |    |

| 3.3.1 COBO On-Board Optic                                                   |    |

| 3.3.2 COBO Optical Link                                                     |    |

| 3.4 Fiber Optic Connectors at the MDI                                       |    |

| 3.4.1 MPO Optical Cable Connections                                         |    |

| 3.4.2 Dual LC Optical Cable connection                                      |    |

| 3.4.3 CS Optical Cable connection                                           |    |

| 3.5 Fiber Optic Lane Assignments at the MDI                                 |    |

| 3.5.1 Electrical data input/output to optical port mapping                  |    |

| 4.0 Mechanical                                                              |    |

| 4.1 Introduction                                                            |    |

| 4.2 Mechanical specification                                                | 55 |

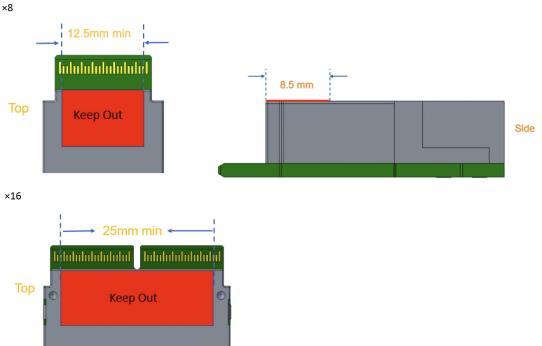

| 4.2.1 ×8 Solution                                                           | 55 |

| 4.2.2 ×16 Solution                                                          |    |

| 4.2.3 OBO Latching to Host Connectors – common to both ×8 and ×16 solutions |    |

| 4.2.4 OBO Insertion, Extraction and Retention Forces                        |    |

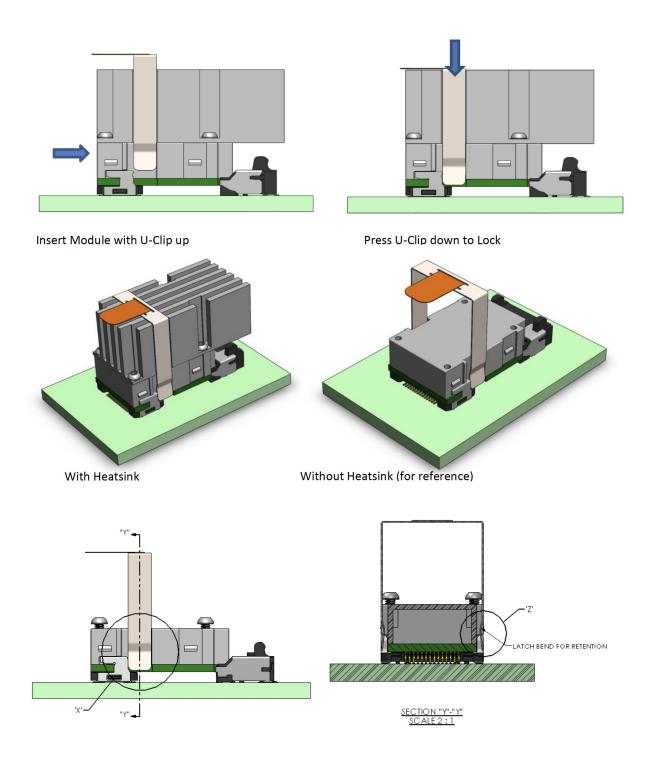

| 4.2.5 Heat Sink Attachment                                                  |    |

| 5.0 Environmental and Thermal                                               |    |

| 5.1 Thermal Requirements                                                    |    |

| 5.2 Thermal Requirements for Tighter Controlled Environments .              |    |

| 6.0 Annex I: Power Supply Noise Measurement                                 |    |

| 6.1 Background                                                              |    |

| 6.2 Modifications to Method Specified in SFF-8431                           |    |

This page is left intentionally blank

# **FIGURES**

| Figure 1-1 –  | COBO Reference Application Example                                                    | 14 |

|---------------|---------------------------------------------------------------------------------------|----|

| Figure 1-2 –  | OBO Configurations                                                                    | 15 |

| Figure 2-1 –  | Electrical Interface with Connectors – Side View                                      | 17 |

| Figure 2-2 –  | COBO Applications Example                                                             | 17 |

| Figure 2-3 –  | Host PCB High-Speed Connector Pads Eight-Lane – Top Side                              | 20 |

| Figure 2-4 –  | OBO PCB High-Speed Connector Pads- Eight-Lane                                         | 21 |

| Figure 2-5 –  | Host PCB High-Speed Connector Pads Sixteen-Lane – Top Side                            | 23 |

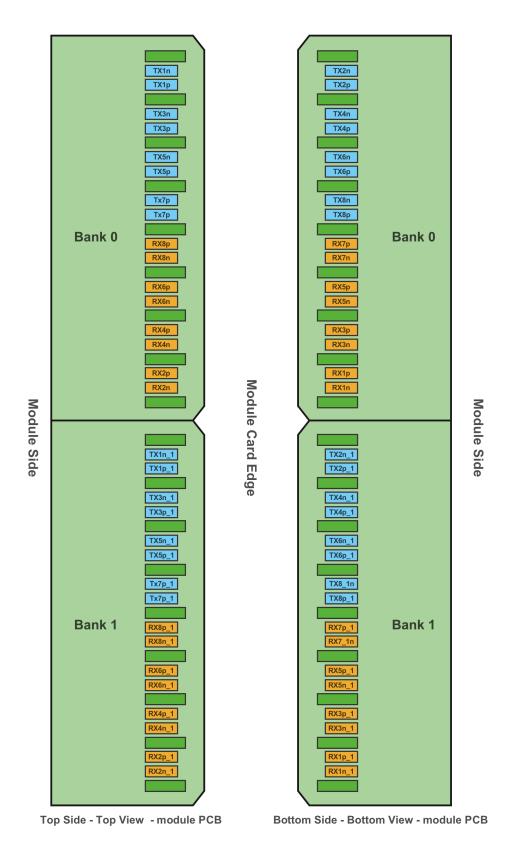

| Figure 2-6 –  | OBO PCB High-Speed Connector Pads- Sixteen-Lane                                       | 24 |

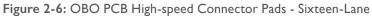

| Figure 2-7 –  | Eight Lane OBO Low-Speed Pins – Paddle Card Bottom Pads                               | 30 |

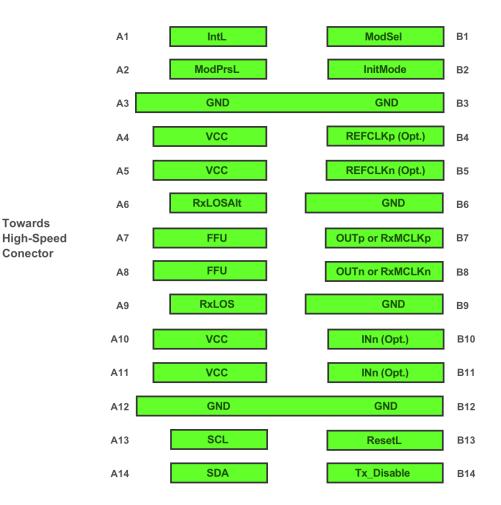

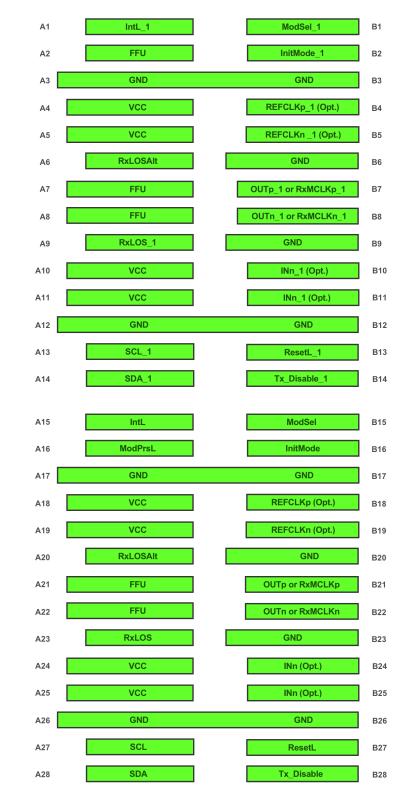

| Figure 2-8 –  | Sixteen Lane OBO Low-Speed Pins – Paddle Card Bottom Pads                             | 32 |

| Figure 2-9 –  | Eight Lane Host High-Speed Schematic Example                                          | 34 |

| Figure 2-10 – | Eight Lane Host Low-Speed Schematic Example                                           | 35 |

| Figure 2-11 – | Sixteen-Lane Host High-Speed Schematic Example                                        | 36 |

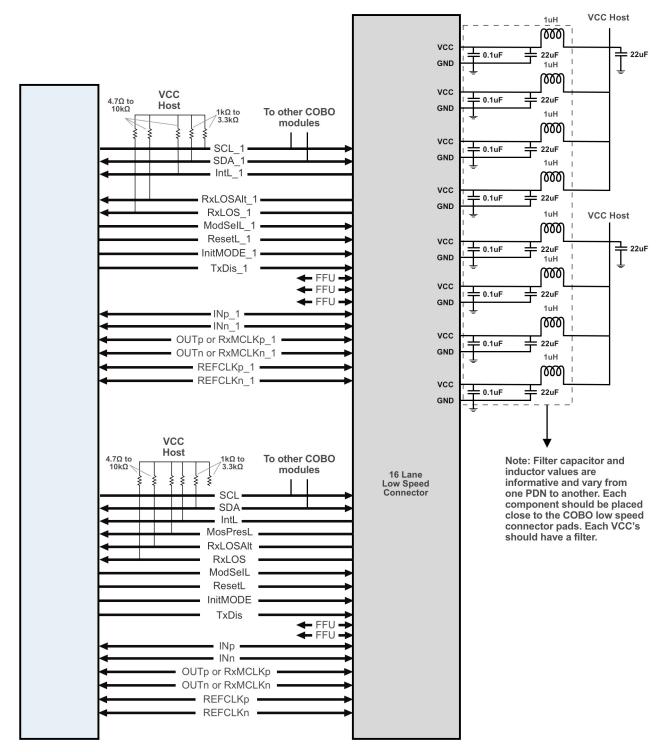

| Figure 2-12 – | Sixteen Lane Host Low-Speed Schematic Example                                         | 37 |

| Figure 2-13 – | TWI Timing Diagram                                                                    | 43 |

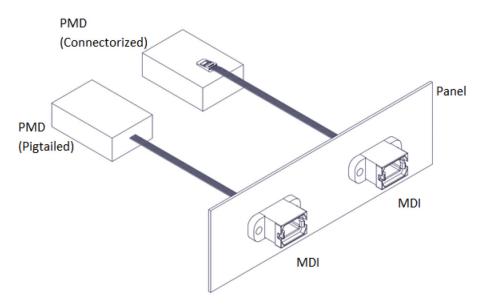

| Figure 3-1 –  | IEEE PMD & MDI Defined Locations For Pigtailed and Connectorized OBOs                 | 45 |

| Figure 3-2 –  | COBO Convention Based on IEEE Definitions                                             | 46 |

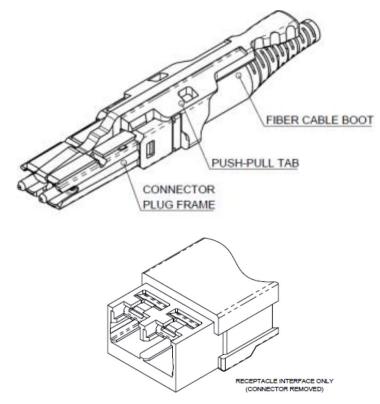

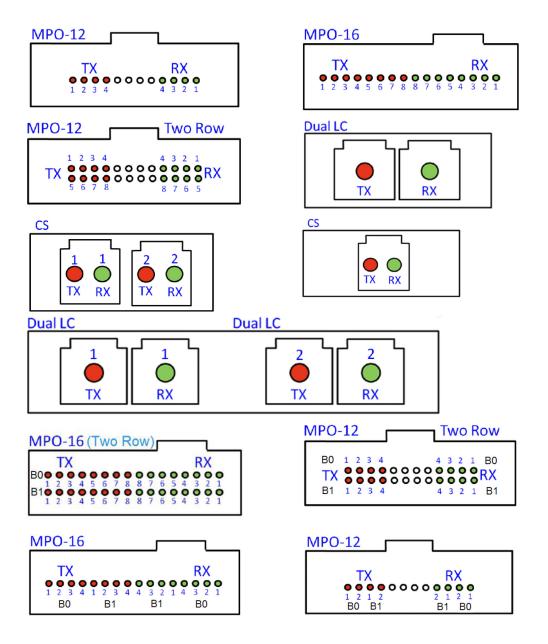

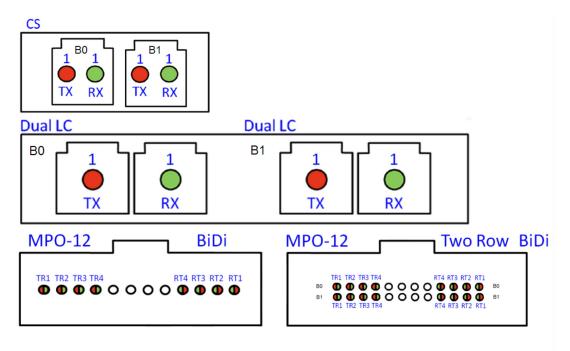

| Figure 3-3 –  | MPO-12 Single Row Optical Patch Cord and OBO Receptacle                               | 47 |

| Figure 3-4 –  | MPO-12 Two Row Optical Patch Cord and OBO Receptacle                                  | 47 |

| Figure 3-5 –  | MPO-16 Single Row Optical Patch Cord and OBO Receptacle                               | 48 |

| Figure 3-6 –  | MPO-16 Two Row Optical Patch Cord and OBO Receptacle                                  | 48 |

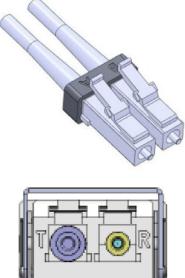

| Figure 3-7 –  | Dual LC Optical Patch Cord and OBO Receptacle                                         | 49 |

| Figure 3-8 –  | CS Optical Patch Cord and OBO Receptacle                                              | 49 |

| Figure 3-9 –  | Fiber Optic Lane Assignments at MDI                                                   | 51 |

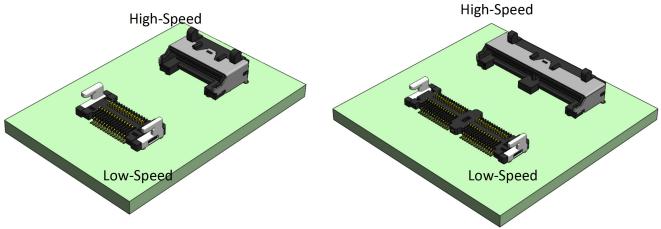

| Figure 4-1 –  | OBO Connector Elements                                                                | 54 |

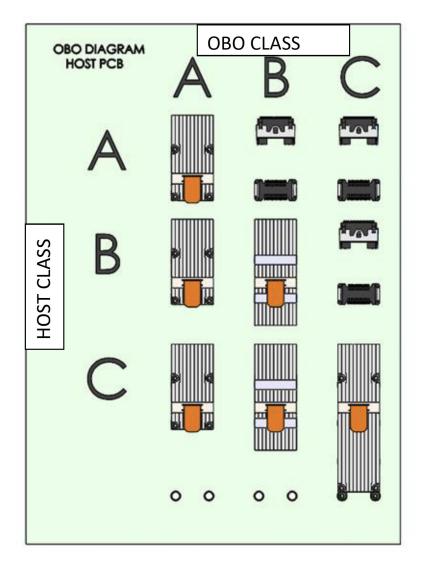

| Figure 4-2 –  | Host-OBO Class Compatibility Chart                                                    | 55 |

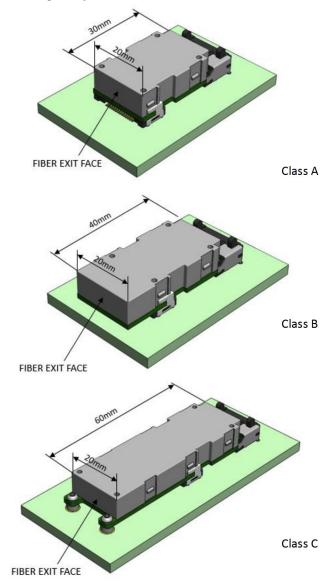

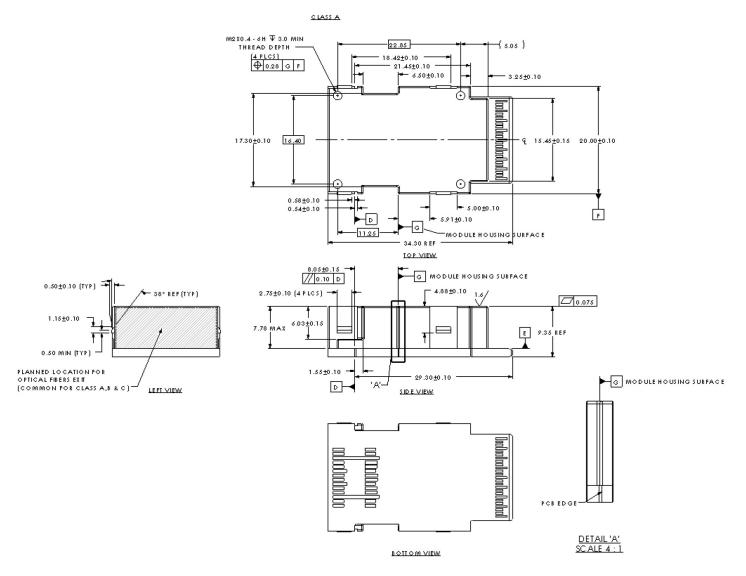

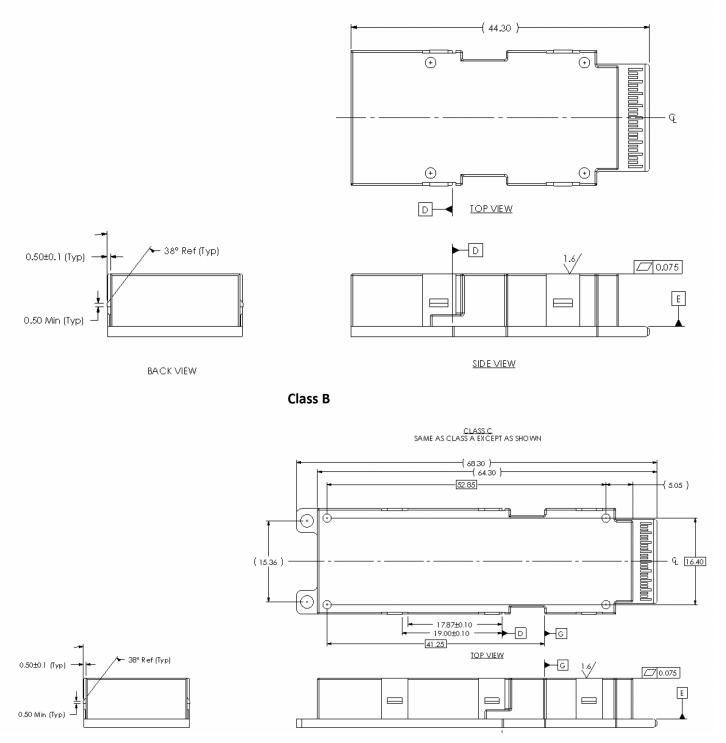

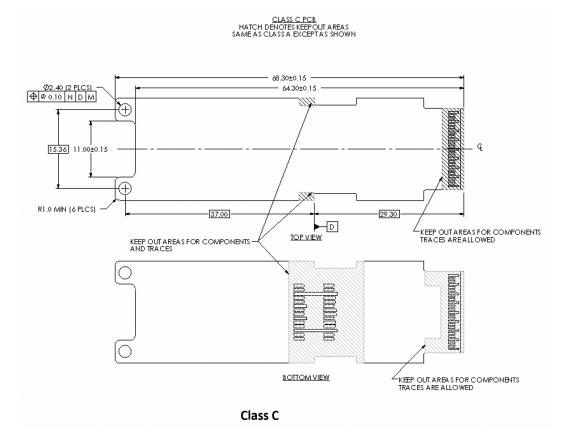

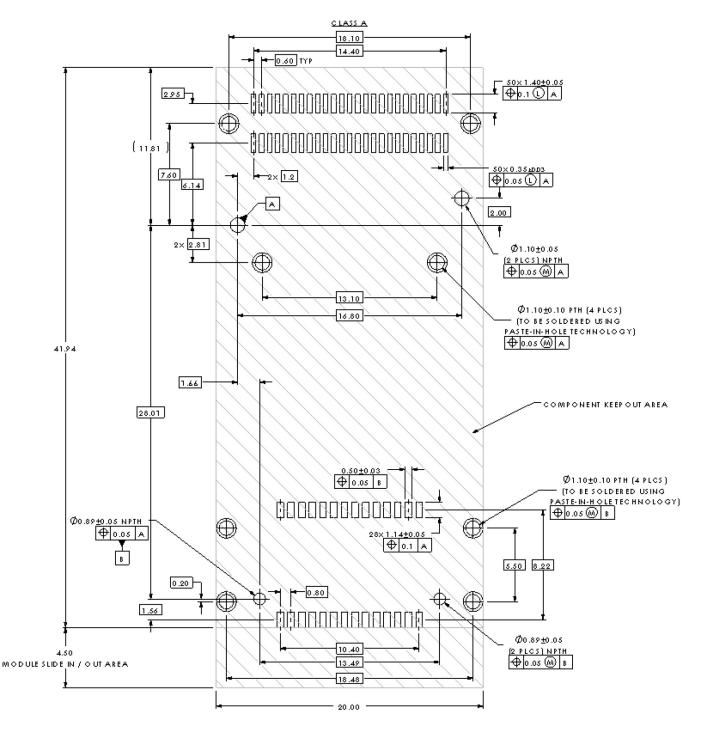

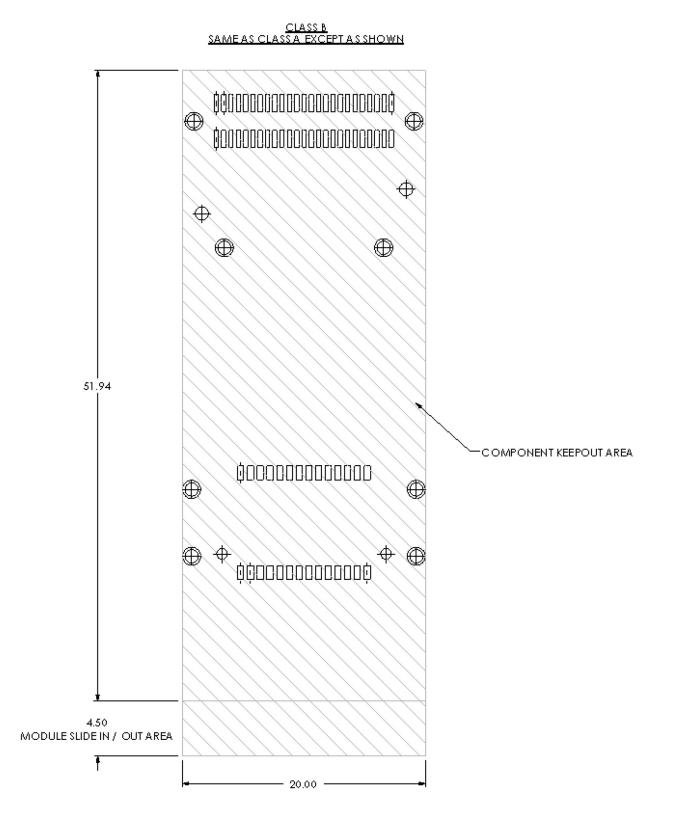

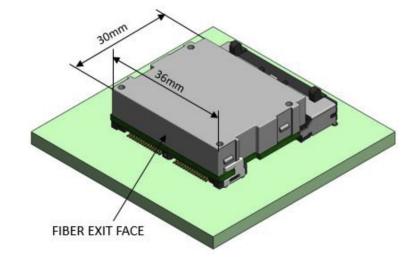

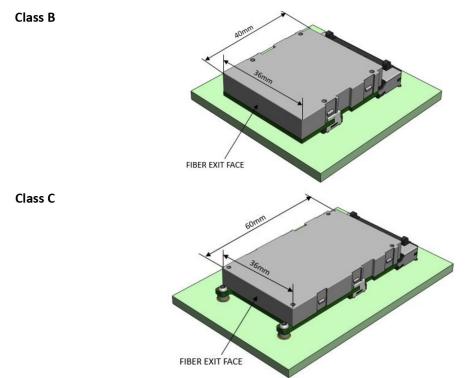

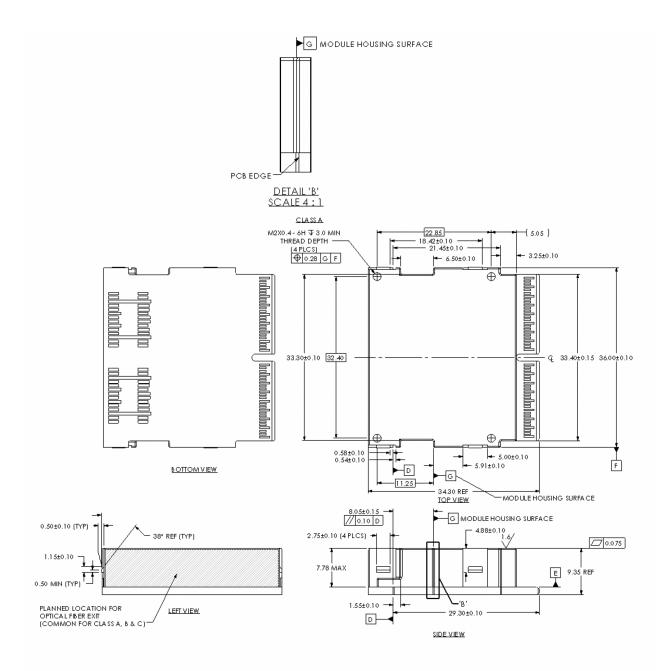

| Figure 4-3 –  | 8-Lane OBO Form Factor - Class A, B, and C                                            | 56 |

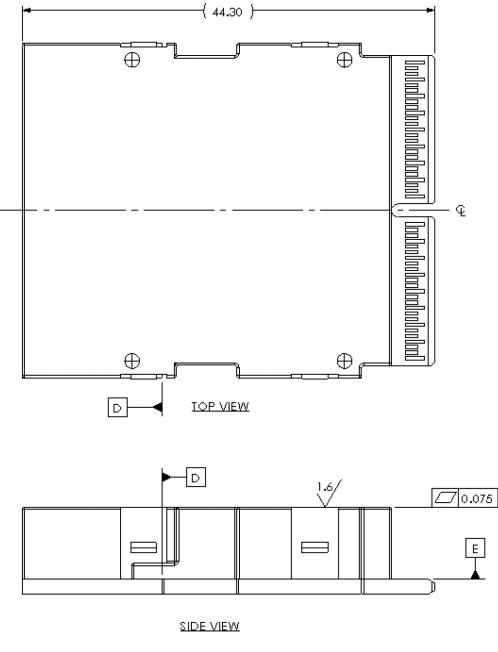

| Figure 4-4 –  | 8-Lane OBO Form Factors, Class A, B, and C                                            | 59 |

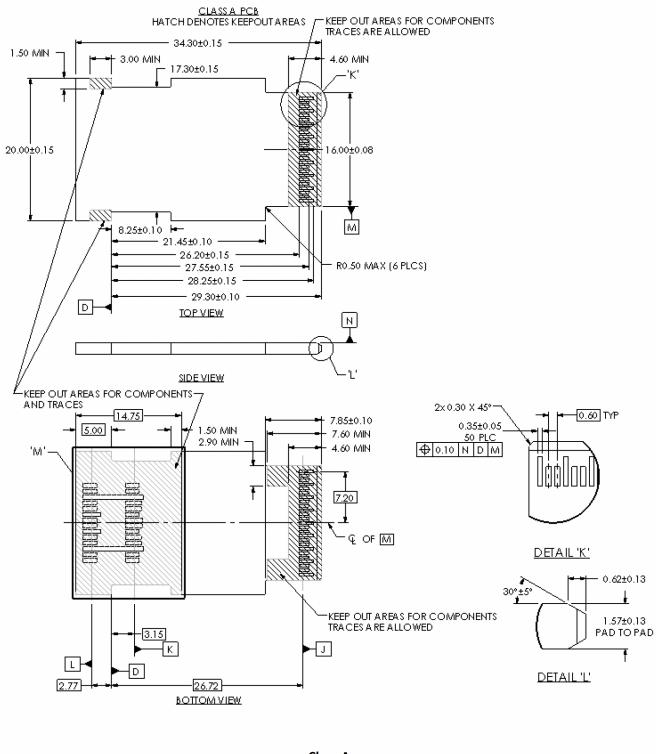

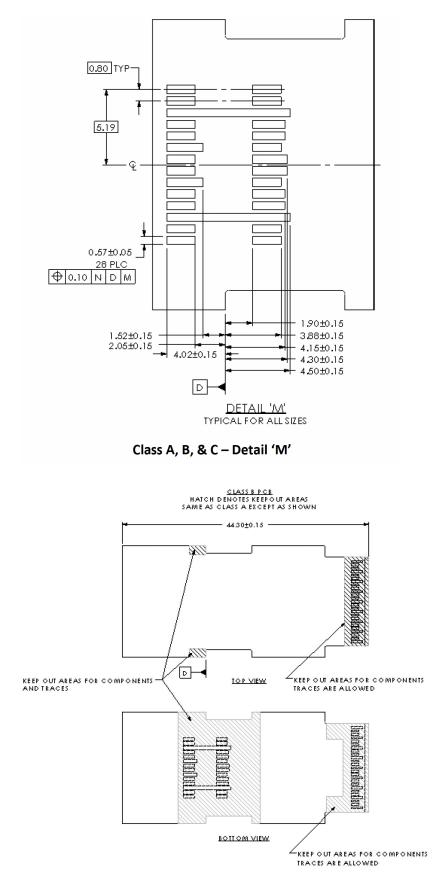

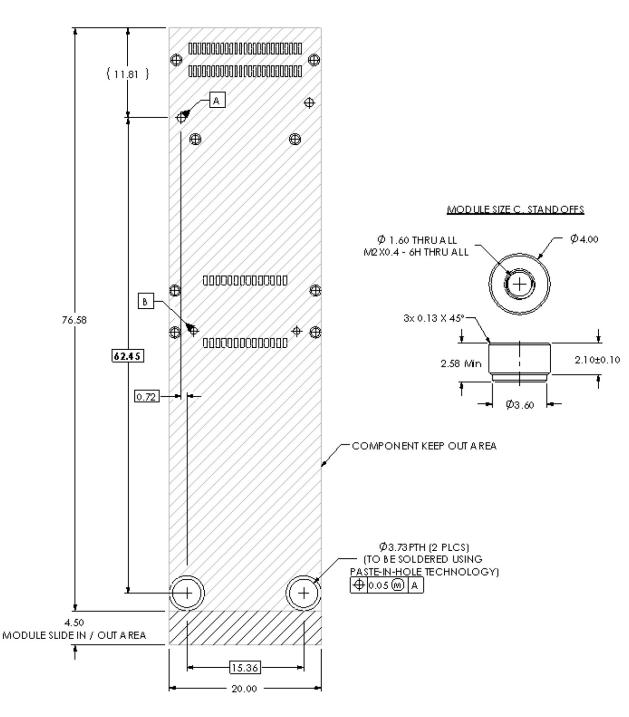

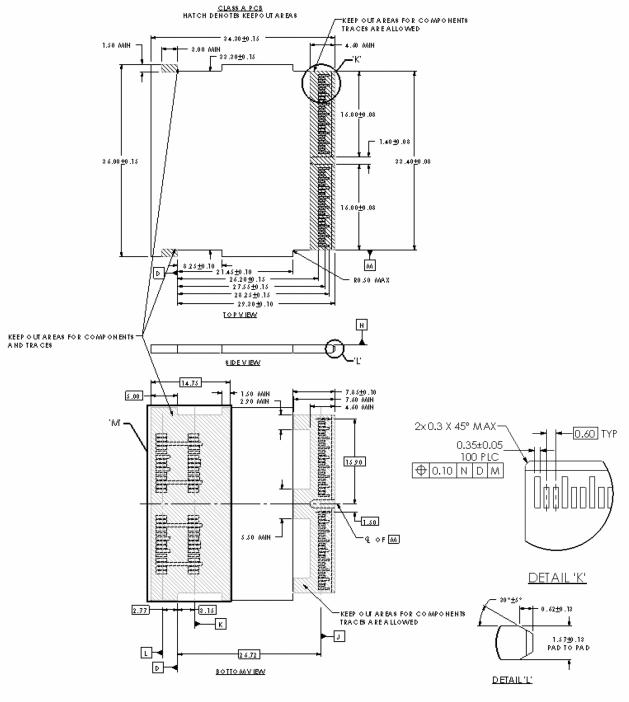

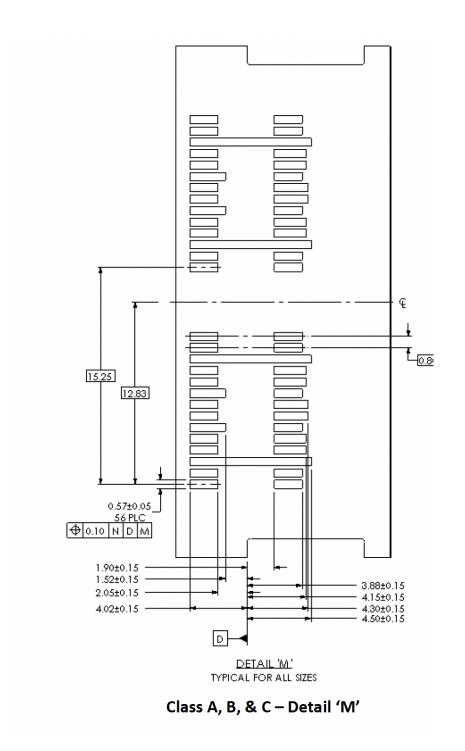

| Figure 4-5 –  | 8-Lane OBO PCB, Class A, B, and C                                                     | 62 |

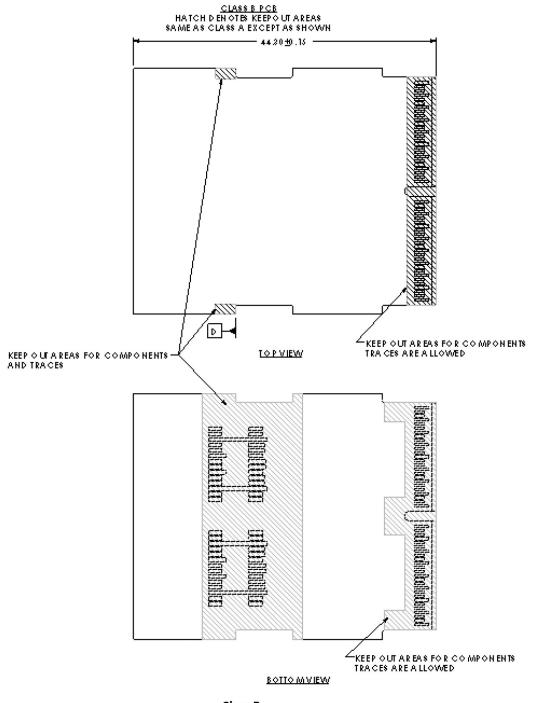

| Figure 4-6 –  | 8-Lane OBO Low-Speed and Power Connector (28 position)                                | 63 |

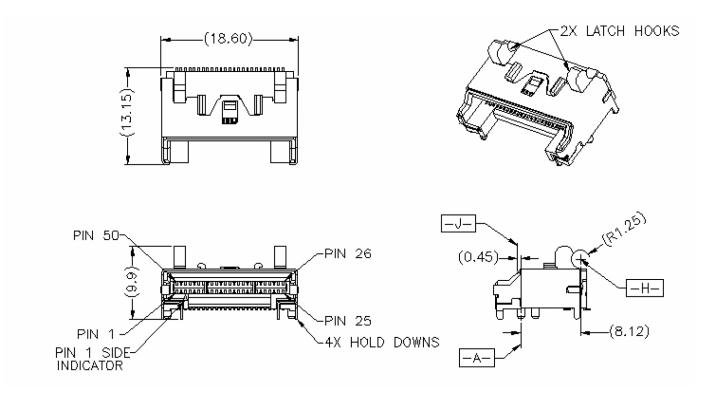

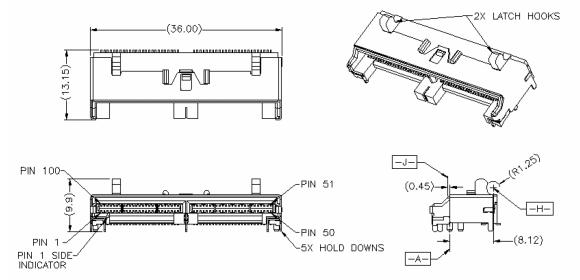

| Figure 4-7 –  | 8-Lane OBO High-Speed (50 position)                                                   | 64 |

| Figure 4-8 –  | Host Board Footprint Supporting Full Pinout as Defined by COBO for 8-Lane Application | 67 |

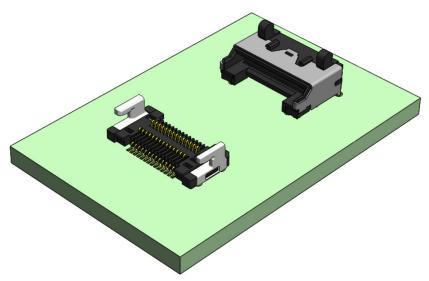

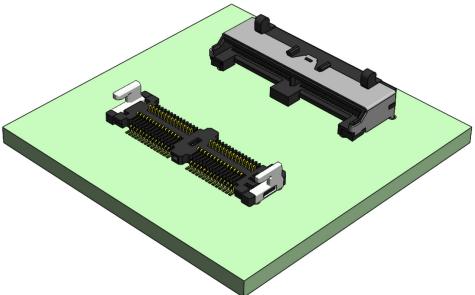

| Figure 4-9 –  | Isometric View of ×8 Connector Solution Set on the Host PCB                           | 68 |

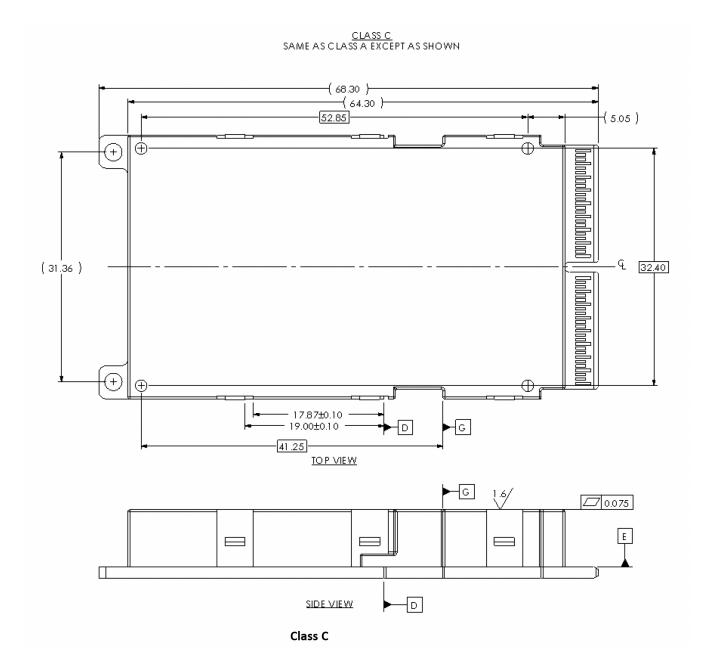

| Figure 4-10 – | 16-Lane OBO Class A, B and C OBOs                                                     | 69 |

| Figure 4-11 – | 16-Lane OBO Form Factors, Class A, B, and C                                           | 72 |

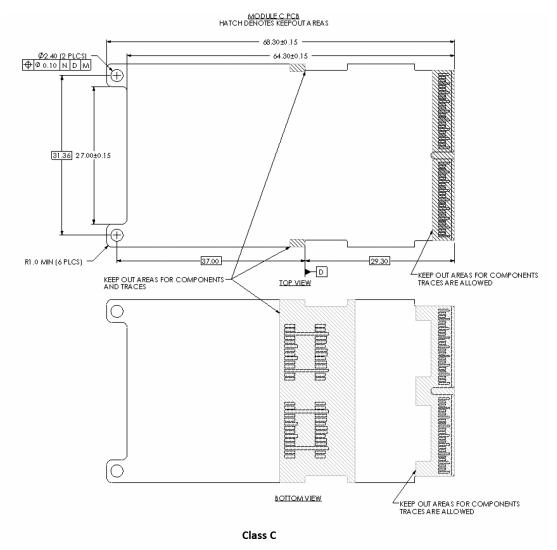

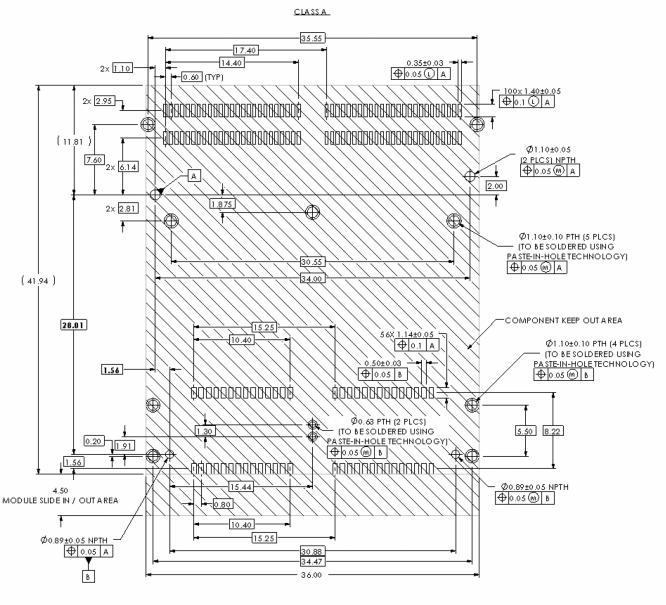

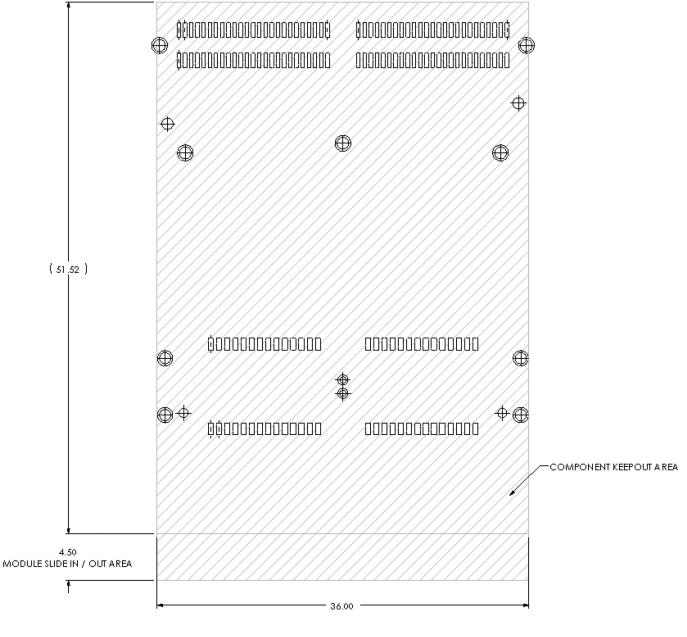

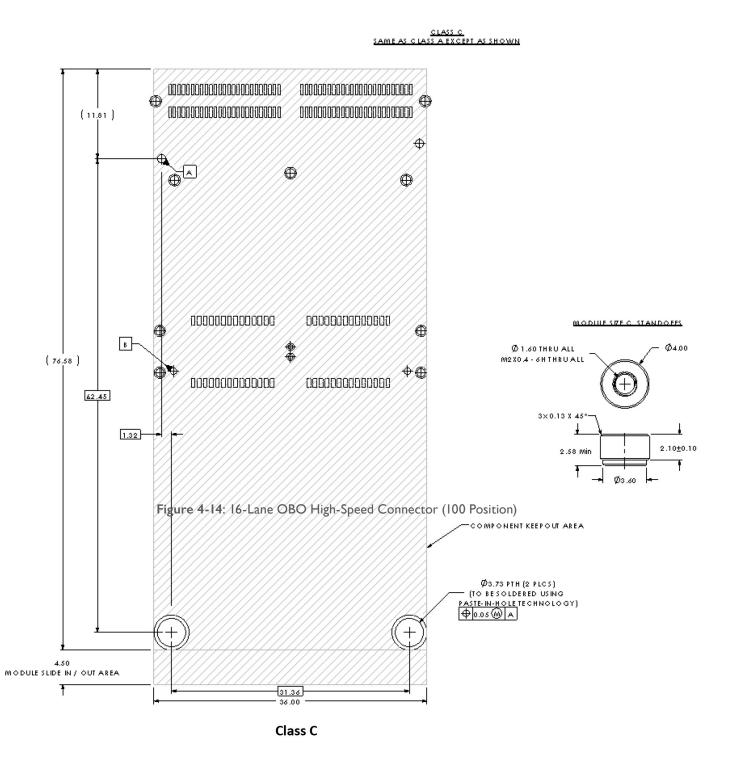

| Figure 4-12 – | 16-Lane OBO PCB, Class A, B, and C                                                    | 76 |

| Figure 4-13 – | 16-Lane OBO Low-Speed and Power Connector (56 position)                               | 77 |

| Figure 4-14 – | 16-Lane OBO High-Speed Connector (100 position)                                       | 77 |

# FIGURES (CON'T)

| Figure 4-15 - Host Board Footprints Supporting Full Pinout as Defined by COBO for 16-Lane applications | 80 |

|--------------------------------------------------------------------------------------------------------|----|

| Figure 4-16 – Isometric View of ×16 Connector Solution Set on the Host PCB                             | 81 |

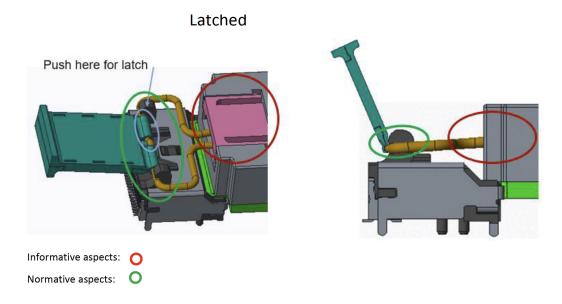

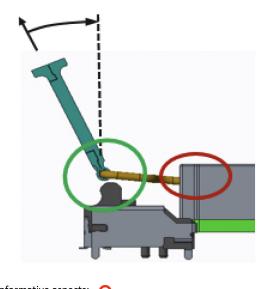

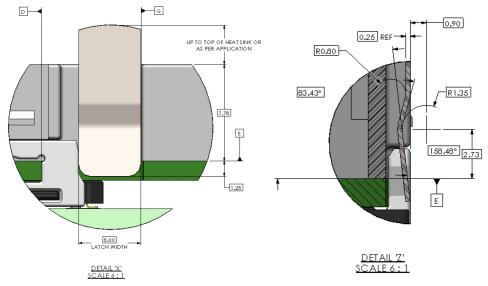

| Figure 4-17 – Latching to the High-Speed Connector and OBO Latch Keep Out Areas                        | 83 |

| Figure 4-18 - High-Speed OBO Latch Dimensions                                                          | 83 |

| Figure 4-19 – Latching to the Low-Speed Connector                                                      | 85 |

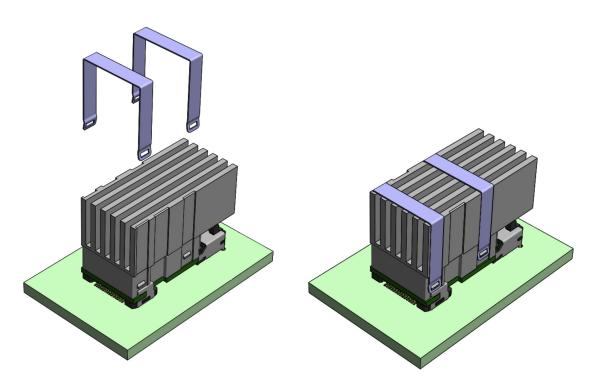

| Figure 4-20 – Heat Sink Attachment by M2 Screw                                                         | 86 |

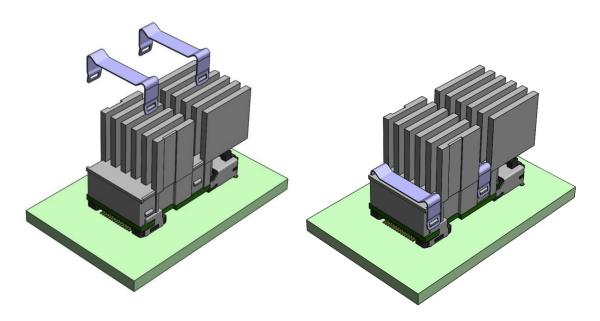

| Figure 4-21 – Heat Sink Attachment By Heat Sink Spring Clip                                            | 87 |

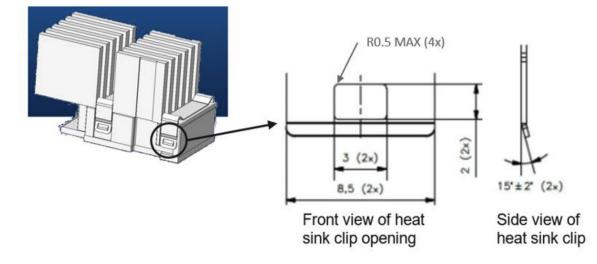

| Figure 4-22 – Heat Sink Clip                                                                           | 87 |

| Figure 6-1 – Power Supply Noise Measurement Location Example                                           |    |

# TABLES

| Table 0-1 – Revision History                                                 |    |

|------------------------------------------------------------------------------|----|

| Table 2-1 – High-Speed Pins– Eight Lane Pin Description                      |    |

| Table 2-2 – High-Speed I/O Pins OBO – Sixteen Lane Pin Description           |    |

| Table 2-3 – Eight Lane Low-Speed Pins                                        |    |

| Table 2-4 – Sixteen Lane Low-Speed Pins                                      |    |

| Table 2-5 – Low-Speed OBO Electrical Specifications.                         |    |

| Table 2-6 – Timing for OBO Soft Control Functions                            |    |

| Table 2-7 – I/O Timing for Squelch and Disable                               |    |

| Table 2-8 – Power Supply Requirements                                        |    |

| Table 2-9 – TWI Management Interface Specifications                          |    |

| Table 3-1 – Electrical Signal to Optical Port Mapping for 8-Lane OBOs (x8)   |    |

| Table 3-2 – Electrical Signal to Optical Port Mapping for 16-Lane OBOs (x16) | 53 |

| Table 4-1 – Datum Structure Used for x8 OBO                                  |    |

| Table 4-2 – Datum Structure Used for x16 OBO                                 | 69 |

| Table 4-3 – OBO Insertion, Extraction and Retention Forces                   | 85 |

| Table 5-1 - Temperature Range Class of operation                             |    |

| Table 5-2 - Temperature Range Classes for Tighter Controlled Applications    |    |

# **TERMS AND DEFINITONS**

| Bank                    | For the I6-lane OBO, a collection of 8 electrical lanes and its corresponding optical lanes                                                                    |  |  |  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| C2M                     | Chip to Module                                                                                                                                                 |  |  |  |

| CDR                     | Clock and Data Recovery                                                                                                                                        |  |  |  |

| CMIS                    | Common Management Interface Specification                                                                                                                      |  |  |  |

| CML                     | Current Mode Logic                                                                                                                                             |  |  |  |

| СОВО                    | Consortium for On-Board Optics                                                                                                                                 |  |  |  |

| Connectorized<br>Module | a PMD with a separable fiber optic connection on the module itself<br>(see also Receptacled module)                                                            |  |  |  |

| Data Center<br>Cabling  | The IEEE defined copper or fiber optic infrastructure between the two MDI points                                                                               |  |  |  |

| Dual LC                 | Dual Lucent Connector                                                                                                                                          |  |  |  |

| Egress                  | Datapath from Host to Media                                                                                                                                    |  |  |  |

| FFU                     | For Future Use                                                                                                                                                 |  |  |  |

| GPIO                    | General Purpose Input Output                                                                                                                                   |  |  |  |

| HS                      | High-Speed                                                                                                                                                     |  |  |  |

| IEEE                    | Institute of Electrical and Electronics Engineers – The IEEE802.3 organization develops standards for Ethernet including the electrical and optical interfaces |  |  |  |

| Ingress                 | Datapath from Media to Host                                                                                                                                    |  |  |  |

| LS                      | Low-Speed                                                                                                                                                      |  |  |  |

| LVCMOS                  | Low Voltage CMOS complementary metal oxide semiconductor                                                                                                       |  |  |  |

| LVTTL                   | Low voltage TTL transistor logic                                                                                                                               |  |  |  |

| MDI                     | Medium Dependent Interface – the IEEE defined link location at which the copper or fiber optic connector mates to the PMD                                      |  |  |  |

| ΜΡΟ                     | Multi-fiber Push-On - Physical contact connector with multiple fibers arranged in a linear array of up two rows. Available in up to twelve fibers per row.     |  |  |  |

| MPO-16                  | Multi-fiber Push-On - Available in up to sixteen fibers per row and up to two rows.<br>Keyed differently to prevent mating with MPO.                           |  |  |  |

| MPO-12                  | MPO connector with 12 fibers                                                                                                                                   |  |  |  |

| MR                      | Medium Reach – An electrical interface capable of supporting ~20dB loss at a frequency of baud rate/2                                                          |  |  |  |

| ово                     | On-Board Optics – an optical transmitter, receiver, or transceiver which is mounted to the interior of the PCBA                                                |  |  |  |

| OIF                     | Optical Internetworking Forum – Develops electrical and optical interoperability agreements                                                                    |  |  |  |

# **TERMS AND DEFINITONS (CON'T)**

| PMD                         | Physical Medium Dependent – the IEEE defined transceiver module minus any copper or fiber optic cabling necessary to take the signal to the card edge              |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pigtailed Module            | A PMD with an inseparable length of fiber, typically terminated with a fiber optic connector, exiting the module and routing to the card edge                      |

| Pluggable<br>Optical Module | An optical transmitter, receiver, or transceiver which gets mounted to the edge of the PCBA                                                                        |

| РСВА                        | Printed Circuit Board Assembly – the printed circuit board along with all the typical components (resistors, capacitors, etc.) soldered in place                   |

| Receptacled<br>Module       | A PMD with a separable fiber optic connection on the module itself (see also Connectorized module)                                                                 |

| RU                          | Rack Unit – A unit of measure describes the height of electronic equipment designed to mount in a 19-inch rack or a 23-inch rack and is 1.75 inches (44.45mm) high |

| ТР2                         | Test Point 2 - The IEEE defined location at which optical power is measured from the source PMD                                                                    |

| ТРЗ                         | Test Point 3 - The IEEE defined location at which optical receive signal is measured going to the destination PMD                                                  |

| тwi                         | Two wire interface used for management interface                                                                                                                   |

| VSR                         | Very Short Reach – An electrical interface capable of supporting a ~10dB loss at a frequency of baud rate/2                                                        |

# REFERENCES

- 1. TIA-604-5, FOCIS 5 Fiber Optic Connector Intermateability Standard Type MPO

- 2. ANSI-TIA-604-18, FOCIS 18 Fiber Optic Connector Intermateability Standard Type MPO- 16

- 3. IEC 61754-7-1, Fibre optic interconnecting devices and passive components Fibre optic connector interfaces Part 7-1: Type MPO connector family One fibre row (similar to FOCIS 5)

- 4. IEC 61754-7-2, Fibre optic interconnecting devices and passive components Fibre optic connector interfaces Part 7-2: Type MPO connector family Two fibre rows (similar to FOCIS 5)

- 5. IEC 61754-7-3, Fibre optic interconnecting devices and passive components Fibre optic connector interfaces Part 7-3: Type MPO connector family Two fibre rows

- 6. IEC 61754-7-4, Fibre optic interconnecting devices and passive components Fibre optic connector interfaces Part 7-4: Type MPO connector family One fibre row

- 7. TIA-604-10, FOCIS 10B Fiber Optic Connector Intermateability Standard- Type LC

- 8. IEC 61754-20, Fibre optic interconnecting devices and passive components Fibre optic connector interfaces Part 20: Type LC connector family (similar to FOCIS 5)

- 9. IEEE Std. 802.3-2015 (IEEE 802.3bm, 100G/40G Ethernet for optical fiber)

- 10. IEEE 802.3bs, 400 Gb/s Ethernet over optical fiber using multiple 25G/50G lane

- 11. SFF-8636, Management Interface for Cabled Environments (Rev 2.7)

- 12. SFF-8665, QSFP+ 28 Gb/s 4X Pluggable Transceiver Solution (QSFP28) (Rev 1.9)

- 13. SFF-8679, QSFP+ 4X Base Electrical Specification (Rev 1.7)

- 14. QSFP-DD Hardware Specification for QSFP Double Density 8X Pluggable Transceiver, Rev 4.0 (Link QSFP-DD MSA)

- 15. Common Management Interface Specification for 8X/16X Pluggable Transceivers, Rev 3.0 (Link QSFP-DD MSA)

- 16. CDFPrev3-0-Mar20-2015-released.pdf, CDFP MSA (Rev 3.0) (Link)

- 17. OIF2014.230.06, CEI-56G-VSR-PAM4 Very Short Reach Interface (Sep 8, 2015)

- 18. OIF2014.245.06, CEI-56G-MR-PAM4 Medium Reach Interface (Sep 10, 2015)

- 19. OIF2014.380.02, CEI-56G-LR-PAM4 Long Reach Interface (Apr 23, 2015)

- 20. SFF-8431, SFP+ 10Gb/s and Low-Speed Electrical Interface

- 21. SFF-8472, Diagnostic Monitoring Interface for Optical Transceivers

- 22. Common Electrical I/O (CEI) Electrical and Jitter Interoperability agreements for 6G+ bps, 11G+ bps and 25G+ bps I/O IA latest version

- 23. GR-253-CORE, Synchronous Optical Network (SONET) Transport Systems: Common Generic Criteria

- 24. GR-63-CORE, NEBS Requirements

- 25. JESD8c.01, Interface Standard for Nominal 3 V/3.3 V Supply Digital Integrated Circuits

- 26. IEEE 802.3bm, 100G/40G Ethernet for optical fiber

- 27. CEI-56G-VSR-PAM4 Very Short Reach Interface, Latest Version

- 28. OIF-Thermal-01.0 Implementation Agreement for Thermal Interface Specification for Pluggable Optics Modules (May 2015)

# Cobo

# **1.** INTRODUCTION

# **1.1 SCOPE**

This specification defines the characteristics of an 8 and 16 lane On-Board Optics (OBOs) for use in up to  $1 \times 400G$  and  $2 \times 400G$  bandwidth capacity applications. and provides a common specification for systems manufacturers, system integrators, component manufacturers, and suppliers of on-board optics.

The specification defines electrical, mechanical, and thermal parameters for an On-Board Optic (OBO). It also includes normative requirements and informative guidance for the optical parameters.

The software management interface (memory map) is not in scope.

# **1.2 DATA CENTER REFERENCE APPLICATION**

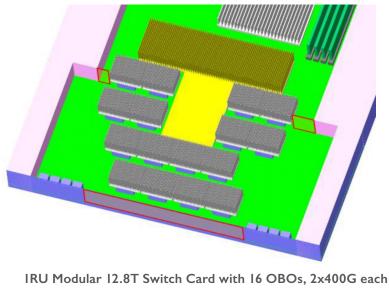

COBO has defined a primary reference application based on a shared generic design. The reference application is defined as an air cooled (with front to back airflow) 1RU modular 12.8T data center switch with one such depiction of a switch card shown in Figure 1-1. Variations on this reference application have been used to determine a number of COBO requirements.

Figure I.I - COBO Reference Application Example

# **1.3 OBO CONFIGURATIONS**

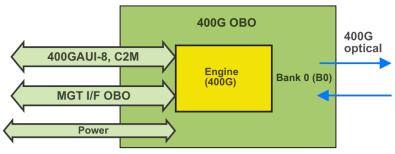

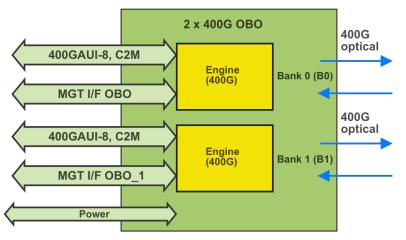

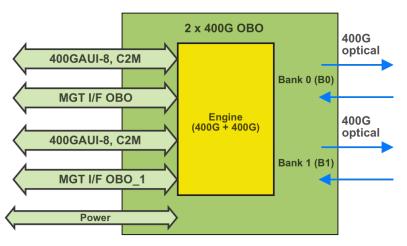

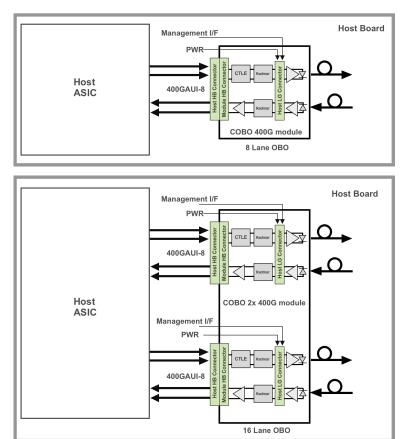

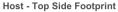

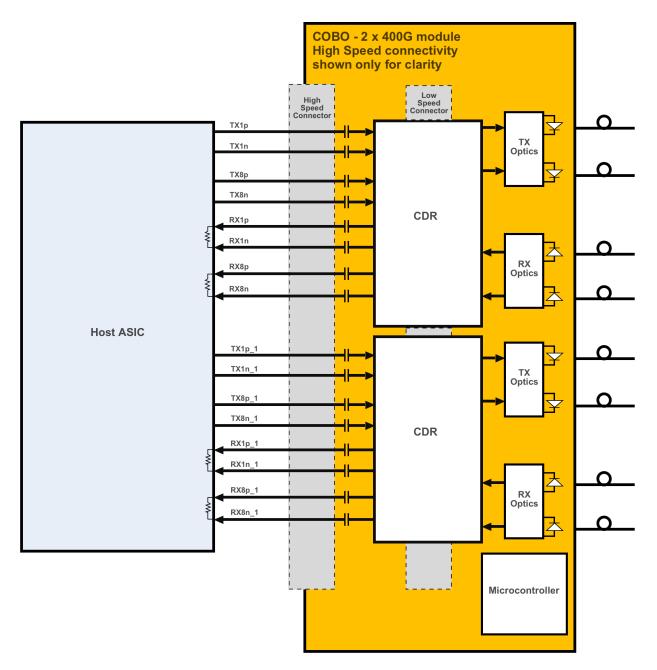

This document considers high density 400G implementations in either a single 400G configuration or a high density 2x400G dual configuration as shown in Figure 1-2.

A: Single 400G Engine (1 x 400G)

B: Dual Independent Engines (2 x 400G)

C: Dual Independent Engine (2 x 400G)

Figure 1.2 - OBO Configurations

Figure 1-2 shows three possible configurations of the 400G OBO. Figure 1-2A shows a single standalone 400G OBO. Figure 1-2B shows a dual 400G implementation where the internal architecture consists of two separate OBO optical engines. Figure 1-2C shows a dual 400G implementation where the internal architecture consists of two 400G optical engines integrated as a single OBO optical engine with two ports.

Figure 1-2B & C enable higher board density layouts by bundling 2 ports of 400G into a single OBO but appears to the host as two separable 400G OBOs.

# **1.4 HIGH-SPEED ELECTRICAL CONFIGURATIONS**

The single OBO, eight-lane, supports eight high-speed data lanes ( $8 \times 25$ GBd PAM4) and the dual OBO, sixteen-lane, supports two independent sets of eight high-speed data lanes ( $2 \times 8 \times 25$ GBd PAM4). The high-speed data interface for the OBO is based on 400GAUI-8 C2M. This document does not preclude usage of other baud rates up to the prescribed 25GBd.

# **1.5 Optical Configurations**

This document does not define the optical physical layer; however, the OBO specification has been developed to be consistent with common industry standards for 400G front-panel pluggable modules.

The OBO may either be pigtailed or connectorized. Optical connectors should comply with industry conventions, see § 3.4.

# **1.6 MANAGEMENT INTERFACE**

The management interface uses the QSFP-DD Common MIS and communicates over a two-wire interface.

The dual OBO configurations shown in Figure 1-2 appear to the host as two separate single 400G optics for both the independent and integrated versions. Therefore, to support 16 optical lanes there are two separate memory maps supported by two independent two-wire interfaces.

# **2. ELECTRICAL SPECIFICATIONS**

# **2.1 - PURPOSE AND APPLICATIONS**

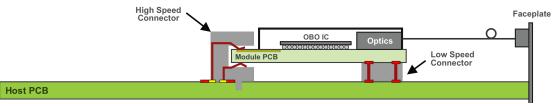

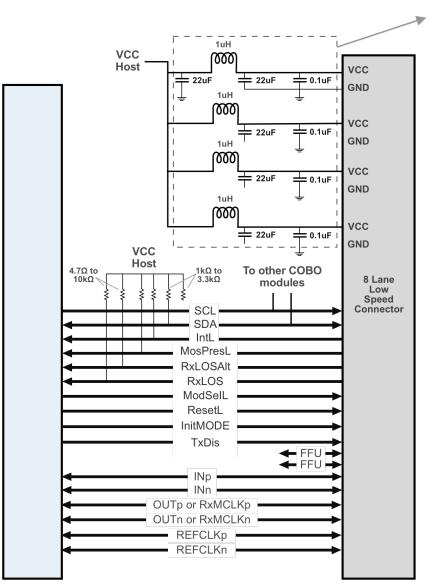

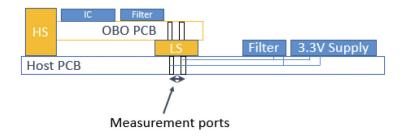

The electrical section specifies the different requirements for eight-lane and sixteen-lane COBO electrical channels which consist of a high-speed and low-speed connector. The electrical section includes the host PCB routing specifications, connector pinout and power supplies specifications. The drawing from Figure 2-1 provide a view of the OBO high-speed and low-speed connectors. The eight-lane and sixteen-lane high-speed connector supports up to eight and sixteen high-speed lanes respectively up to 25GBd. The eight-lane and sixteen-lane low-speed connector supports 28 and 56 contacts respectively for power and I/O's.

FIGURE 2.1 - Electrical Interface with Connectors - Side View

This section defines;

- · High-speed and low-speed connector pinout and signal definitions

- Power supplies and return specifications

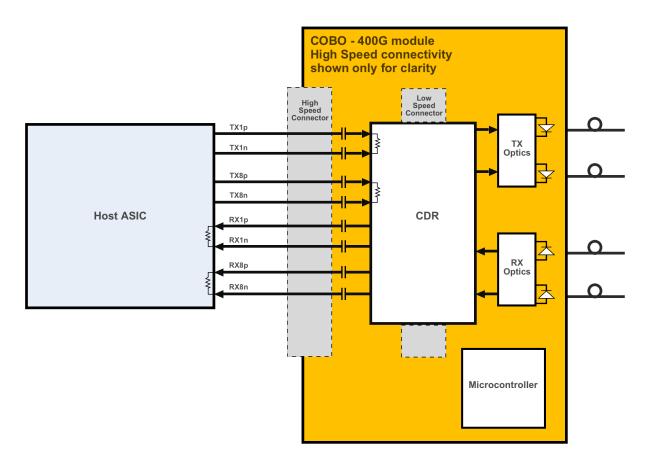

Figure 2-2 shows examples of block diagrams representing the different applications of OBOs.

FIGURE 2.2 - COBO Applications Example

# **2.2 CLOCKING CONSIDERATIONS**

## **2.2.1 DATA PATH DESCRIPTION**

Within an OBO, host electrical and OBO media lanes are grouped together into a logical concept called a data path. A data path is intended to represent a group of lanes that will be powered up or down and initialized together. An example would include a 400GAUI-8 to 400GBASE-DR4 OBO implementation, where the data path would include eight host electrical lanes and four OBO media lanes.

#### **2.2.2 Tx Clocking Considerations**

Within a given Tx data path, the host is responsible for ensuring that all electrical lanes delivered to the OBO are frequency synchronous (sourced from the same clock domain). If an OBO supports multiple Tx data paths running concurrently, the different Tx data paths can either all be in a single clock domain or separate clock domains. The OBO advertises which of these two modes it supports via the management registers.

If the OBO supports multiple Tx data paths running concurrently in a single clock domain, the OBO shall ensure that active Tx data paths continue to operate undisturbed even as other Tx data paths (and their associated Tx input lanes) are enabled/disabled by the host.

#### **2.2.3 Rx Clocking Considerations**

Within a given Rx data path, all lanes received on the OBO media interface are required to be frequency synchronous (sourced from the same clock domain). If an OBO supports multiple Rx data paths running concurrently, the OBO shall allow the different Rx data paths to be asynchronous from each other (sourced from separate clock domains).

## **2.3 Electrical Connector – High-Speed**

This section contains signal definitions and requirements that are specific to the OBO. The high-speed I/O's includes the connections between the host ASIC and OBO. The 400GAUI-8 C2M, interface support both 1 x 400G and 2 x 400G. For more information, see the appropriate electrical specifications for the electrical link, e.g., 802.3ba Annex 86A, 802.3bs Annex 120E or Annex 120C, FC-PI-6, FC-PI-7, OIF-CEI-28G-VSR, OIF-CEI-56G-VSR or the InfiniBand specification.

Partial or complete squelch specifications may be provided in the appropriate specification. Where squelch is not fully defined by the appropriate specification, the recommendations of the following subsections 2.3.1 and 2.3.2 may be used.

### 2.31 Rx(N) (P/N)

Rx(n)(p/n) are OBO receiver data outputs. Rx(n)(p/n) are AC-coupled 100 $\Omega$  differential lines that should be terminated with 100 $\Omega$  differentially at the Host ASIC. The AC coupling is inside the OBO and not required on the Host board. When properly terminated, the differential voltage swing shall be less than or equal to the limit in the relevant standard, whichever is less.

Output squelch for loss of optical input signal, hereafter RX Squelch, is required and shall function as follows. In the event of the Rx input signal on any optical port becoming equal to or less than the level required to assert LOS, then the receiver data output(s) associated with that Rx port shall be squelched. A single Rx optical port can be associated with more than one Rx output as shown in §3.5.1;

- Rx1n/p to Rx8n/p is referred to Bank 0 for the eight-lane or sixteen-lane OBO.

- Rx1n/p\_1 to Rx8n/p\_1 is referred to Bank 1 for the sixteen-lane OBO

In the squelched state, output impedance levels are maintained while the differential voltage amplitude shall be less than 50 mVpp. In normal operation the default case has RX Squelch active. Rx Squelch can be deactivated using Rx Squelch Disable through the TWI. For specific details refer to CMIS latest version.

## 2.3.2 Tx(N)(P/N)

Tx(n)(p/n) are OBO transmitter data inputs. Tx(n)(p/n) are AC-coupled 100 $\Omega$  differential lines with 100 $\Omega$  differential terminations inside the OBO. The AC coupling is inside the OBO and not required on the Host board. The input signal complies with the relevant standard at the OBO input.

Output squelch, hereafter Tx Squelch, for loss of electrical signal, hereafter Tx LOS, is an optional function. Where implemented it shall function as follows. In the event of the differential, peak-to-peak electrical signal amplitude on any electrical input channel becoming less than 70 mVpp, then the transmitter optical output associated with that electrical input channel shall be squelched and the associated TxLOS flag set. If multiple electrical input channels are associated with the same optical output channel, see § 3.5.1, the loss of any of the incoming electrical input channels causes the optical output channel to be squelched;

- Tx1n/p to Tx8n/p is referred to Bank 0 for the eight-lane or sixteen-lane OBO.

- $Tx1n/p_1$  to  $Tx8n/p_1$  is referred to Bank 1 for the sixteen-lane OBO.

For applications, e.g. Ethernet, where the transmitter off condition is defined in terms of average power, squelching by disabling the transmitter is recommended and for applications, e.g. InfiniBand, where the transmitter off condition is defined in terms of OMA, squelching the transmitter by setting the OMA to a low level is recommended.

In OBO operation, where Tx Squelch is implemented, the default case has Tx Squelch active. Tx Squelch can be deactivated using Tx Squelch Disable through the TWI. Tx Squelch is an optional function. If TX squelch is implemented, the disable squelch must be provided. For specific details refer to CMIS latest version.

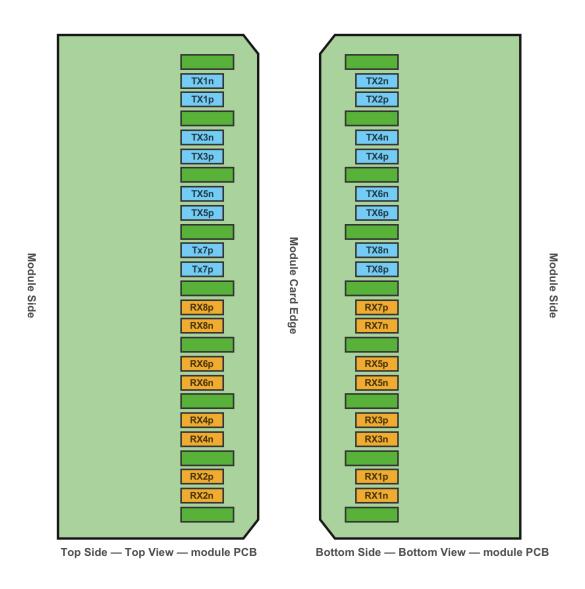

### 2.3.3 EIGHT-LANE HIGH-SPEED PINS

The eight-lane high-speed edge connector consists of a single paddle card with 25 pads on the top and 25 pads on the bottom of the paddle card for a total of 50 pads.

See Figure 2-3 for the host top side pads signal symbols.

The pads are designed for a sequenced mating:

First mate - ground pads

Second mate - signal pads

See Figure 2-4 for the OBO pad numbering.

Refer to Table 2-1 for more pad description and Figure 4-15 for pad dimensions.

| 26 | GND      |           | GND      | 25 |                     |

|----|----------|-----------|----------|----|---------------------|

| 27 | Rx2n     |           | Rx1n     | 24 |                     |

| 28 | Rx2p     |           | Rx1p     | 23 |                     |

| 29 | GND      |           | GND      | 22 |                     |

| 30 | Rx4n     |           | Rx3n     | 21 |                     |

| 31 | Rx4p     |           | Rx3p     | 20 |                     |

| 32 | GND      |           | GND      | 19 |                     |

| 33 | Rx6n     |           | Rx5n     | 18 |                     |

| 34 | Rx6p     |           | Rx5p     | 17 |                     |

| 35 | GND      |           | GND      | 16 |                     |

| 36 | Rx8n     |           | Rx7n     | 15 |                     |

| 37 | Rx8p     |           | Rx7p     | 14 | Towards             |

| 38 | GND      |           | GND      | 13 | Low Speed Connector |

| 39 | Тх7р     |           | Tx8p     | 12 |                     |

| 40 | Tx7n     |           | Tx8n     | 11 |                     |

| 41 | GND      |           | GND      | 10 |                     |

| 42 | Tx5p     |           | Тх6р     | 9  |                     |

| 43 | Tx5n     |           | Tx6n     | 8  |                     |

| 44 | GND      |           | GND      | 7  |                     |

| 45 | Тх3р     |           | Tx4p     | 6  |                     |

| 46 | Tx3n     |           | Tx4n     | 5  |                     |

| 47 | GND      |           | GND      | 4  |                     |

| 48 | Tx1p     |           | Tx2p     | 3  |                     |

| 49 | Tx1n     |           | Tx2n     | 2  |                     |

| 50 | GND      |           | GND      | 1  |                     |

| ·  | Host - T | op Side F | ootprint | -  |                     |

Figure 2-3: Host PCB High-Speed Connector Pads Eight-Lane - Top Side

Figure 2-4: OBO PCB High-Speed Connector Pads - Eight-Lane

| Host<br>Pad | OBO<br>Pad | Symbol | Description                      | Interface |

|-------------|------------|--------|----------------------------------|-----------|

| I           | I          | GND    | Ground                           |           |

| 2           | 2          | Tx2N   | Transmit Inverted Data Input     | CML-I     |

| 3           | 3          | Tx2P   | Transmit Non-Inverted Data Input | CML-I     |

| 4           | 4          | GND    | Ground                           |           |

| 5           | 5          | Tx4N   | Transmit Inverted Data Input     | CML-I     |

| 6           | 6          | Tx4P   | Transmit Non-Inverted Data Input | CML-I     |

| 7           | 7          | GND    | Ground                           |           |

| 8           | 8          | Tx6N   | Transmit Inverted Data Input     | CML-I     |

| 9           | 9          | Tx6P   | Transmit Non-Inverted Data Input | CML-I     |

| 10          | 10         | GND    | Ground                           |           |

| 11          | 11         | Tx8N   | Transmit Inverted Data Input     | CML-I     |

| 12          | 12         | Tx8P   | Transmit Non-Inverted Data Input | CML-I     |

| 13          | 13         | GND    | Ground                           |           |

| 14          | 14         | Rx7P   | Receive Non-Inverted Data Input  | CML-O     |

| 15          | 15         | Rx7N   | Receive Inverted Data Input      | CML-O     |

| 16          | 16         | GND    | Ground                           |           |

| 17          | 17         | Rx5P   | Receive Non-Inverted Data Input  | CML-O     |

| 18          | 18         | Rx5N   | Receive Inverted Data Input      | CML-O     |

| 19          | 19         | GND    | Ground                           |           |

| 20          | 20         | Rx3P   | Receive Non-Inverted Data Input  | CML-O     |

| 21          | 21         | Rx3N   | Receive Inverted Data Input      | CML-O     |

| 22          | 22         | GND    | Ground                           |           |

| 23          | 23         | RxIP   | Receive Non-Inverted Data Input  | CML-O     |

| 24          | 24         | RxIN   | Receive Inverted Data Input      | CML-O     |

| 25          | 25         | GND    | Ground                           |           |

| 26          | 26         | GND    | Ground                           |           |

| 27          | 27         | Rx2N   | Receive Inverted Data Input      | CML-O     |

| 28          | 28         | Rx2P   | Receive Non-Inverted Data Input  | CML-O     |

| 29          | 29         | GND    | Ground                           |           |

| 30          | 30         | Rx4N   | Receive Inverted Data Input      | CML-O     |

| 31          | 31         | Rx4P   | Receive Non-Inverted Data Input  | CML-O     |

| 32          | 32         | GND    | Ground                           |           |

| 33          | 33         | Rx6N   | Receive Inverted Data Input      | CML-O     |

| 34          | 34         | Rx6P   | Receive Non-Inverted Data Input  | CML-O     |

| 35          | 35         | GND    | Ground                           |           |

| 36          | 36         | Rx8N   | Receive Inverted Data Input      | CML-O     |

| 37          | 37         | Rx8P   | Receive Non-Inverted Data Input  | CML-O     |

| 38          | 38         | GND    | Ground                           |           |

| 39          | 39         | Tx7P   | Transmit Non-Inverted Data Input | CML-I     |

| 40          | 40         | Tx7N   | Transmit Inverted Data Input     | CML-I     |

| 41          | 41         | GND    | Ground                           |           |

| 42          | 42         | Tx5P   | Transmit Non-Inverted Data Input | CML-I     |

| 43          | 43         | Tx5N   | Transmit Inverted Data Input     | CML-I     |

| 44          | 44         | GND    | Ground                           |           |

| 45          | 45         | Tx3P   | Transmit Non-Inverted Data Input | CML-I     |

| 46          | 46         | Tx3N   | Transmit Inverted Data Input     | CML-I     |

| 47          | 47         | GND    | Ground                           |           |

| 48          | 48         | TxIP   | Transmit Non-Inverted Data Input | CML-I     |

| 49          | 49         | TxIN   | Transmit Inverted Data Input     | CML-I     |

| 50          | 50         | GND    | Ground                           |           |

Tabel 2-1: High-Speed Pins - Eight-Lane Pin Description

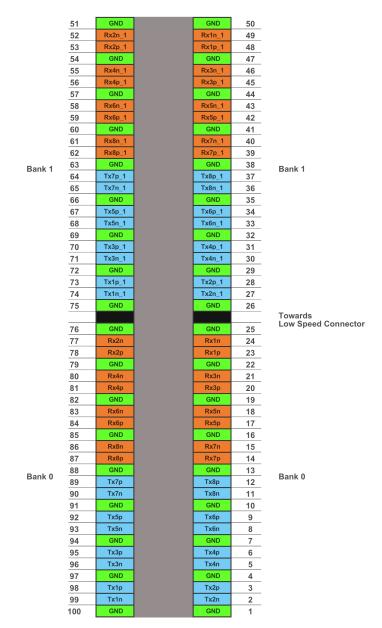

#### 2.3.4 SIXTEEN-LANE HIGH-SPEED PINS

The sixteen-lane high-speed edge connector consists of a single paddle card with 50 pads on the top and 50 pads on the bottom of the paddle card for a total of 100 pads.

Figure 2-5 for the host top side pads signal symbols

The pads are designed for a sequenced mating:

First mate - ground pads

Second mate - signal pads

See Figure 2-6 for the OBO pad numbering.

Refer to Table 2-2 for more pad description and Figure 4-15 for pad dimensions.

Figure 2-5: Host PCB High-Speed Connector Pads Sixteen-Lane - Top Side

| Host<br>Pad | OBO<br>Pad | Symbol           | Description                      | Bank | Interface |

|-------------|------------|------------------|----------------------------------|------|-----------|

|             |            | -                |                                  |      | Interface |

|             |            | GND              | Ground                           | 0    | CML I     |

| 2           | 2          | Tx2n             | Transmit Inverted Data Input     | 0    | CML-I     |

| 3           | 3          | Tx2p             | Transmit Non-Inverted Data Input | 0    | CML-I     |

| 4           | 4          | GND              | Ground                           | 0    | 01411     |

| 5           | 5          | Tx4n             | Transmit Inverted Data Input     | 0    | CML-I     |

| 6           | 6          | Tx4p             | Transmit Non-Inverted Data Input | 0    | CML-I     |

| 7           | 7          | GND              | Ground                           | 0    |           |

| 8           | 8          | Tx6n             | Transmit Inverted Data Input     | 0    | CML-I     |

| 9           | 9          | Тх6р             | Transmit Non-Inverted Data Input | 0    | CML-I     |

| 10          | 10         | GND              | Ground                           | 0    |           |

| 11          | 11         | Tx8n             | Transmit Inverted Data Input     | 0    | CML-I     |

| 12          | 12         | Тх8р             | Transmit Non-Inverted Data Input | 0    | CML-I     |

| 13          | 13         | GND              | Ground                           | 0    |           |

| 14          | 14         | Rx7p             | Receive Non-Inverted Data Input  | 0    | CML-O     |

| 15          | 15         | Rx7n             | Receive Inverted Data Input      | 0    | CML-O     |

| 16          | 16         | GND              | Ground                           | 0    |           |

| 17          | 17         | R×5p             | Receive Non-Inverted Data Input  | 0    | CML-O     |

| 18          | 18         | Rx5n             | Receive Inverted Data Input      | 0    | CML-O     |

| 19          | 19         | GND              | Ground                           | 0    |           |

| 20          | 20         | Rx3p             | Receive Non-Inverted Data Input  | 0    | CML-O     |

| 21          | 21         | Rx3n             | Receive Inverted Data Input      | 0    | CML-O     |

| 22          | 22         | GND              | Ground                           | 0    |           |

| 23          | 23         | Rxlp             | Receive Non-Inverted Data Input  | 0    | CML-O     |

| 24          | 24         | RxIn             | Receive Inverted Data Input      | 0    | CML-O     |

| 25          | 25         | GND              | Ground                           | 0    |           |

| 26          | 26         | GND              | Ground                           | 1    |           |

| 27          | 27         | Tx2n I           | Transmit Inverted Data Input     | I    | CML-I     |

| 28          | 28         | Tx2p_I           | Transmit Non-Inverted Data Input |      | CML-I     |

| 29          | 29         | GND              | Ground                           | 1    |           |

| 30          | 30         | Tx4n I           | Transmit Inverted Data Input     |      | CML-I     |

| 31          | 31         | Tx4p I           | Transmit Non-Inverted Data Input | 1    | CML-I     |

| 32          | 32         | GND              | Ground                           | 1    |           |

| 33          | 33         | Tx6n I           | Transmit Inverted Data Input     | 1    | CML-I     |

| 34          | 34         | Tx6p I           | Transmit Non-Inverted Data Input | 1    | CML-I     |

| 35          | 35         | GND              | Ground                           | 1    |           |

| 36          | 36         | Tx8n I           | Transmit Inverted Data Input     | 1    | CML-I     |

| 37          | 37         | Tx8p_I           | Transmit Non-Inverted Data Input | i.   | CML-I     |

| 38          | 38         | GND              | Ground                           | 1    |           |

| 39          | 39         | Rx7p_I           | Receive Non-Inverted Data Input  | i.   | CML-O     |

| 40          | 40         | Rx7n I           | Receive Inverted Data Input      | 1    | CML-O     |

| 41          | 41         | GND              | Ground                           | 1    | 0.12 0    |

| 42          | 42         | Rx5p_I           | Receive Non-Inverted Data Input  |      | CML-O     |

| 43          | 43         | Rx5p_1<br>Rx5n I | Receive Inverted Data Input      |      | CML-O     |

| 44          | 44         | GND              | Ground                           |      |           |

| 45          | 45         | Rx3p I           | Receive Non-Inverted Data Input  | 1    | CML-O     |

| 46          | 46         | Rx3p_1           | Receive Inverted Data Input      |      | CML-O     |

| 46          | 46         | GND              | Ground                           | 1    | CHL-O     |

| 47          | 47         |                  | Receive Non-Inverted Data Input  | 1    | CML-O     |

|             |            | Rxlp_l           |                                  | 1    |           |

| 49          | 49         | RxIn_I           | Receive Inverted Data Input      |      | CML-O     |

| 50          | 50         | GND              | Ground                           |      |           |

| 51          | 51         | GND              | Ground                           | I    | CMLO      |

| 52          | 52         | Rx2n_I           | Receive Inverted Data Input      |      | CML-O     |

| 53          | 53         | Rx2p_I           | Receive Non-Inverted Data Input  | 1    | CML-O     |

| 54          | 54         | GND              | Ground                           |      |           |

| 55          | 55         | Rx4n_I           | Receive Inverted Data Input      | I    | CML-O     |

| 56          | 56         | Rx4p_I           | Receive Non-Inverted Data Input  |      | CML-O     |

Table 2-2: -High-Speed I/O Pins OBO - Sixteen Lane Pin Description

| F 7 | - 7 | CNID   |                                  |   |       |

|-----|-----|--------|----------------------------------|---|-------|

| 57  | 57  | GND    | Ground                           |   | CML O |

| 58  | 58  | Rx6n_I | Receive Inverted Data Input      | 1 | CML-O |

| 59  | 59  | Rx6p_I | Receive Non-Inverted Data Input  |   | CML-O |

| 60  | 60  | GND    | Ground                           | I |       |

| 61  | 61  | Rx8n_I | Receive Inverted Data Input      | 1 | CML-O |

| 62  | 62  | Rx8p_I | Receive Non-Inverted Data Input  | I | CML-O |

| 63  | 63  | GND    | Ground                           |   |       |

| 64  | 64  | Tx7p_I | Transmit Non-Inverted Data Input | I | CML-I |

| 65  | 65  | Tx7n_I | Transmit Inverted Data Input     | I | CML-I |

| 66  | 66  | GND    | Ground                           | 1 |       |

| 67  | 67  | Tx5p_l | Transmit Non-Inverted Data Input | I | CML-I |

| 68  | 68  | Tx5n_I | Transmit Inverted Data Input     | I | CML-I |

| 69  | 69  | GND    | Ground                           | I |       |

| 70  | 70  | Tx3p_I | Transmit Non-Inverted Data Input | I | CML-I |

| 71  | 71  | Tx3n_I | Transmit Inverted Data Input     | I | CML-I |

| 72  | 72  | GND    | Ground                           | I |       |

| 73  | 73  | Txlp_l | Transmit Non-Inverted Data Input | I | CML-I |

| 74  | 74  | TxIn_I | Transmit Inverted Data Input     | I | CML-I |

| 75  | 75  | GND    | Ground                           | I |       |

| 76  | 76  | GND    | Ground                           | 0 |       |

| 77  | 77  | Rx2n   | Receive Inverted Data Input      | 0 | CML-O |

| 78  | 78  | Rx2p   | Receive Non-Inverted Data Input  | 0 | CML-O |

| 79  | 79  | GND    | Ground                           | 0 |       |

| 80  | 80  | Rx4n   | Receive Inverted Data Input      | 0 | CML-O |

| 81  | 81  | Rx4p   | Receive Non-Inverted Data Input  | 0 | CML-O |

| 82  | 82  | GND    | Ground                           | 0 |       |

| 83  | 83  | Rx6n   | Receive Inverted Data Input      | 0 | CML-O |

| 84  | 84  | Rx6p   | Receive Non-Inverted Data Input  | 0 | CML-O |

| 85  | 85  | GND    | Ground                           | 0 |       |

| 86  | 86  | Rx8n   | Receive Inverted Data Input      | 0 | CML-O |

| 87  | 87  | Rx8p   | Receive Non-Inverted Data Input  | 0 | CML-O |

| 88  | 88  | GND    | Ground                           | 0 |       |

| 89  | 89  | Tx7p   | Transmit Non-Inverted Data Input | 0 | CML-I |

| 90  | 90  | Tx7n   | Transmit Inverted Data Input     | 0 | CML-I |

| 91  | 91  | GND    | Ground                           | 0 |       |

| 92  | 92  | Tx5p   | Transmit Non-Inverted Data Input | 0 | CML-I |

| 93  | 93  | Tx5n   | Transmit Inverted Data Input     | 0 | CML-I |

| 94  | 94  | GND    | Ground                           | 0 |       |

| 95  | 95  | Тх3р   | Transmit Non-Inverted Data Input | 0 | CML-I |

| 96  | 96  | Tx3n   | Transmit Inverted Data Input     | 0 | CML-I |

| 97  | 97  | GND    | Ground                           | 0 |       |

| 98  | 98  | Txlp   | Transmit Non-Inverted Data Input | 0 | CML-I |

| 99  | 99  | TxIn   | Transmit Inverted Data Input     | 0 | CML-I |

| 100 | 100 | GND    | Ground                           | 0 |       |

|     |     | 0.10   | e. ouild                         | ~ |       |

Table 2-2: – High-Speed I/O Pins OBO - Sixteen Lane Pin Description (con't)

# **2.4 Electrical Connector – Low-Speed**

The low-speed connector for the eight-lane and sixteen lane OBO has the following low-speed pins for control, power and status to support the different OBO applications. The definitions are for eight-lane and sixteen-lane low-speed definitions.

- Bank 0 of the sixteen-lane uses the same definitions as the eight-lane.

- Bank 1 of the sixteen-lane uses the suffix "\_1".

## 2.4.1.1 RxLOS

The RxLOS signal is intended as an indication to the host in which the OBO is installed that the primary port optical input signal strength is below a certain threshold.

RxLOS may be an optional function depending on the supported standard. If the RxLOS function is not implemented, or is reported via the two-wire interface only, the RxLOS contact shall be held low using a pull down of  $1k\Omega$  by the OBO. This pin can be useful for SyncE applications.

The RxLOS is an open drain/collector output from the OBO and for a nominally 3.3V VCC, the resistive pull up to VCC on the Host shall be in the range  $4.7k\Omega$  to  $10k\Omega$ .

Rx\_LOS assert min (ton\_rxdis) and de-assert max (toff\_rxdis) are defined in the relevant standard. Sixteen-lane uses RXLOS and RXLOS\_1.

#### 2.4.1.2 RESETL

ResetL is an input control to the OBO. A low level on the ResetL pin longer than the minimum pulse length (t\_RE-SET\_init) initiates an OBO module reset and all user OBO settings to their default state.

The ResetL shall be pulled up to VCC in the OBO. Sixteen-lane uses ResetL and ResetL\_1.

### 2.4.1.3 MODSELL

The ModSelL is an input signal. When held low by the host, the OBO communication interface is active on the single TWI bus. When ModSelL is "High", the OBO shall not respond to or acknowledge any TWI communication from the host.

In order to avoid conflicts, the host system shall not attempt TWI communications within the ModSelL de-assert time after any OBO modules are deselected. Similarly, the host must wait at least for the period of the ModSelL assert time before communicating with the newly selected OBO. The assertion and de-asserting periods of different OBOs may overlap as long as the above timing requirements are met.

The ModSelL shall be pulled up to VCC in the OBO. Sixteen-lane uses ModSelL and ModselL\_1.

### 2.4.1.4 INTL

Interrupt request from OBO to host is an output signal. When the IntL is asserted low, it indicates a change in the OBO state, a possible OBO operational fault or a status critical to the host system. The host identifies the source of the interrupt using the TWI or other communication channel. The IntL signal is deasserted High after all set interrupt flags are read.

The signal is an open collector output and must be pulled up to VCC Host on the host board.

Sixteen lane uses IntL and IntL\_1.

## 2.4.1.5 OUTP/OUTN OR RXMCLKP/RXMCLKN

The signals are CML outputs. Example illustrative function could either be used for a low frequency output differential clock; RxMCLKp/n, in phase with the primary optical port Rx data. This can be useful for SyncE applications. Or another illustrative example could be a faster communication channel, OUTp/n, support.

Sixteen-lane uses:

OUTp/OUTn or RxMCLKp/RxMCLKn and OUTp\_1/OUTn\_1 or RxMCLKp\_1/RxMCLKn\_1.

### 2.4.1.6 INP/INN

INp and INn are differential CML inputs. Example illustrative function could be a faster communication channel support.

The inputs shall be AC coupled inside the OBO.

Sixteen-lane uses INp/INn and INp\_1/INn\_1.

#### 2.4.1.7 MosPrsL

ModPrsL must be pulled up to VCC Host on the host board and pulled low in the OBO. The ModPrsL is asserted "Low" by the OBO when the OBO is inserted.

ModPrsL must be pulled up to VCC Host with a resistor in the range of 4.7k to 10k on the host board and pulled low in the OBO.

Sixteen-lane uses one ModPrsL.

### 2.4.1.8 Tx\_DISABLE

When Tx\_Disable is asserted high or left open, the OBO's transmitter output shall be turned off. When the TX\_Disable is asserted low, the OBO's transmitter is operating normally.

TX\_Disable signal shall be pulled up to VCC in the OBO.

Sixteen-lane uses Tx\_Disable and Tx\_Disable\_1.

#### 2.4.1.9 RxLOSALT

The RXLOSAlt output signal is intended as an indication to the host in which the OBO is installed that a secondary port optical input signal strength is below a certain threshold. This can be useful for SyncE applications.

The RxLOSAlt is an open drain/collector output from the OBO.

For a nominally 3.3V VCC, the resistive pull up to VCC on the Host shall be in the range 4.7k to 10k.

Sixteen-lane uses RxLOSAlt and RxLOSAlt\_1.

## **2.4.1.10 INITMODE**

The InitMode signal allows the host to define whether the OBO will initialize under host software control (InitMode asserted High) or hardware control (InitMode deasserted Low).

The InitMode input signal shall be pulled up to VCC inside the OBO.

See "CMIS xx-xx" for more information.

Sixteen-lane uses InitMODE and InitMODE\_1.

### 2.4.1.11 SCL

2-wire serial clock signal. Requires pull-up to 3.3V on host.

Sixteen-lane uses SCL and SCL\_1.

Refer to § 2.6 for further details.

## 2.4.1.12 SDA

2-wire serial data signal. Requires pull-up to 3.3V on host.

Sixteen-lane uses SDA and SDA\_1.

Refer to § 2.6 for further details.

### 2.4.1.13 REFCLKP/REFCLKN

The REFCLKp and REFCLKn are CML input clocks. The purpose of the input reference clock is to act as a low jitter transmit reference.

Sixteen-lane uses REFCLKp/REFCLKn and REFCLKp\_1/REFCLKn\_1.

For application requiring different transmitter clock sources, egress direction, the OBO shall report clock recovery capabilities.

See latest CMIS "TX input clock recover capabilities" for further details.

#### 2.4.1.14 VCC

3.3V nominal supply.

Each low-speed connector pins provides up to 1.5 amps for a total of 6 amps (19.8 watts nominal).

Refer to § 2.4.

### 2.4.1.15 RETURN (GND)

OBO Ground. Logic and power return path.

## 2.4.2 EIGHT AND SIXTEEN LOW-SPEED PIN LOCATIONS

The OBO eight-lane low-speed connector consists of 28 pads on the bottom. The pads are defined in such a manner to accommodate insertion of an OBO into an OBO receptacle.

Refer to Figure 2-7 and Table 2-3 for more information.

The OBO sixteen-lane low-speed connector consists of 56 pads on the bottom. The pads are defined in such a manner to accommodate insertion of an OBO into an OBO receptacle.

Refer to Figure 2-8 and Table 2-4 for more information.

The pads are designed for a sequenced mating:

• First mate – ground pads

Eight Lane: Extended between A3-B3 and A12-B12. See Figure 2-7

Sixteen Lane: Extended between A3-B3, A12-B12, A17-B17 and A26-B26. See Figure 2-8.

- Second mate VCC pads

- Third mate signal pads

Table 2-7: Eight Lane OBO Low-Speed Pins – Paddle Card Bottom Pads

| Host | OBO |                 |                                                      |      |            |

|------|-----|-----------------|------------------------------------------------------|------|------------|

| Pad  | Pad | Symbol          | Description                                          | Bank | Interface  |

| AI   | AI  | IntL            | Interrupt                                            | 0    | LVTTL-O    |

| A2   | A2  | ModPrsL         | OBO Presence                                         | 0    | LVTTL-O    |

| A3   | A3  | GND             | Return                                               | 0    |            |

| A4   | A4  | VCC             | +3.3V Power Supply                                   | 0    |            |

| A5   | A5  | VCC             | +3.3V Power Supply                                   | 0    |            |

| A6   | A6  | RxLOSAlt        | Receiver Loss of Signal Alternate                    | 0    | LVTTL-O    |

| A7   | A7  | FFU             | For Future Use                                       | 0    |            |

| A8   | A8  | FFU             | For Future Use                                       | 0    |            |

| A9   | A9  | RxLOS           | Receiver Loss of Signal                              | 0    | LVTTL-O    |

| AI0  | AI0 | VCC             | +3.3V Power Supply                                   | 0    |            |

| All  | All | VCC             | +3.3V Power Supply                                   | 0    |            |

| AI2  | AI2 | GND             | Return                                               | 0    |            |

| AI3  | AI3 | SCL             | Two-wire serial interface clock                      | 0    | LVCMOS I/O |

| AI4  | AI4 | SDA             | Two-wire serial interface data                       | 0    | LVCMOS I/O |

|      |     |                 |                                                      |      |            |

| BI   | BI  | ModSel          | OBO Select                                           | 0    | LVTTL-I    |

| B2   | B2  | InitMode        | Initialization Mode                                  | 0    | LVTTL-I    |

| B3   | B3  | GND             | Return                                               | 0    |            |

| B4   | B4  | REFCLKp (opt)   | Reference Clock p – Optional                         | 0    | CML-I      |

| B5   | B5  | REFCLKn (opt)   | Reference Clock n – Optional                         | 0    | CML-I      |

| B6   | B6  | GND             | Return                                               | 0    |            |

| B7   | B7  | OUTp or RxMCLKp | Communication Output p or Clock Monitor p– Optional  | 0    | CML-O      |

| B8   | B8  | OUTn or RxMCLKn | Communication Output n or Clock Monitor n – Optional | 0    | CML-O      |

| B9   | B9  | GND             | Return                                               | 0    |            |

| B10  | B10 | INp (opt)       | Communication Input p – Optional                     | 0    | CML-I      |

| BII  | BII | Inn (opt)       | Communication Input n – Optional                     | 0    | CML-I      |

| B12  | B12 | GND             | Return                                               | 0    |            |

| BI3  | BI3 | ResetL          | OBO RESET                                            | 0    | LVTTL-I    |

| B14  | BI4 | Tx_Disable      | Transmit Disable                                     | 0    | LVTTL-I    |

Table 2.3: Eight Lane Low-Speed Pins

Table 2-8: Sixteen Lane OBO Low-Speed Pins – Paddle Card Bottom Pads

Towards High-Speed Conector

| Host                                                                                                                                                                      | ОВО                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                  |                                                                                                                                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pad                                                                                                                                                                       | Pad                                                                                                                                                                       | Symbol                                                                                                                                                                                                                                                                                                                                                                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Bank                                                                                             | Interface                                                                                                                                                                                             |

| Al                                                                                                                                                                        | AI                                                                                                                                                                        | IntL_I                                                                                                                                                                                                                                                                                                                                                                        | Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                  | LVTTL-O                                                                                                                                                                                               |

| A2                                                                                                                                                                        | A2                                                                                                                                                                        | FFU                                                                                                                                                                                                                                                                                                                                                                           | For Future Use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                  | LVTTL-O                                                                                                                                                                                               |

| A3                                                                                                                                                                        | A3                                                                                                                                                                        | GND                                                                                                                                                                                                                                                                                                                                                                           | Return                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1                                                                                                |                                                                                                                                                                                                       |